- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19591 > EPM7032BTI44-5 (Altera)IC MAX 7000 CPLD 32 44-TQFP PDF資料下載

參數(shù)資料

| 型號: | EPM7032BTI44-5 |

| 廠商: | Altera |

| 文件頁數(shù): | 4/66頁 |

| 文件大小: | 0K |

| 描述: | IC MAX 7000 CPLD 32 44-TQFP |

| 標準包裝: | 480 |

| 系列: | MAX® 7000B |

| 可編程類型: | 系統(tǒng)內(nèi)可編程 |

| 最大延遲時間 tpd(1): | 5.0ns |

| 電壓電源 - 內(nèi)部: | 2.375 V ~ 2.625 V |

| 邏輯元件/邏輯塊數(shù)目: | 2 |

| 宏單元數(shù): | 32 |

| 門數(shù): | 600 |

| 輸入/輸出數(shù): | 36 |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 44-TQFP |

| 供應商設備封裝: | 44-TQFP(10x10) |

| 包裝: | 托盤 |

第1頁第2頁第3頁當前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁

12

Altera Corporation

MAX 7000B Programmable Logic Device Data Sheet

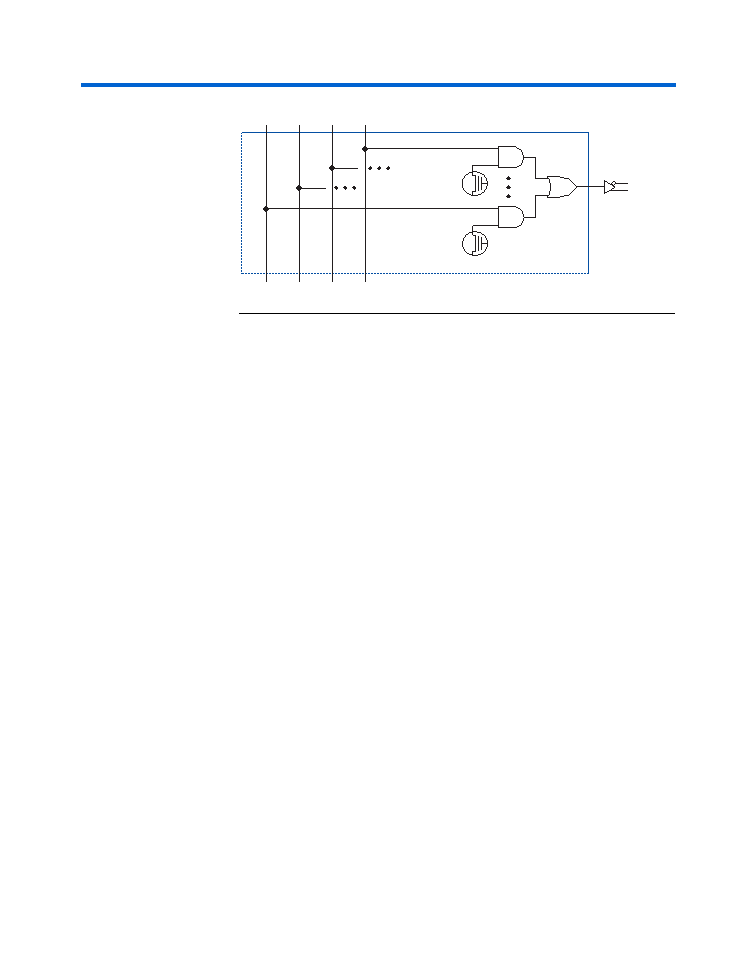

Figure 5. MAX 7000B PIA Routing

While the routing delays of channel-based routing schemes in masked or

field-programmable gate arrays (FPGAs) are cumulative, variable, and

path-dependent, the MAX 7000B PIA has a predictable delay. The PIA

makes a design’s timing performance easy to predict.

I/O Control Blocks

The I/O control block allows each I/O pin to be individually configured

for input, output, or bidirectional operation. All I/O pins have a tri-state

buffer that is individually controlled by one of the global output enable

control block for MAX 7000B devices. The I/O control block has

six or ten global output enable signals that are driven by the true or

complement of two output enable signals, a subset of the I/O pins, or a

subset of the I/O macrocells.

To LAB

PIA Signals

相關PDF資料 |

PDF描述 |

|---|---|

| NDL1215SC | CONV DC/DC 2W 12VIN 15VOUT SIP |

| VI-B01-CY-F3 | CONVERTER MOD DC/DC 12V 50W |

| ECC08DCSD | CONN EDGECARD 16POS DIP .100 SLD |

| LC51024VG-10F676I | IC XPLD 1024MC 10NS 676FPBGA |

| ABC31DRYN-S734 | CONN EDGECARD 62POS DIP .100 SLD |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| EPM7032BUC49-3 | 制造商:Altera Corporation 功能描述:IC MAX |

| EPM7032BUC49-3N | 功能描述:CPLD - 復雜可編程邏輯器件 CPLD - MAX 7000 32 Macro 41 IOs RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM7032BUC49-5 | 制造商:Altera Corporation 功能描述:CPLD MAX 7000B Family 600 Gates 32 Macro Cells 212.8MHz 2.5V 49-Pin UFBGA 制造商:Altera Corporation 功能描述:IC MAX |

| EPM7032BUC49-7 | 制造商:Altera Corporation 功能描述:IC MAX |

| EPM7032JC44-10 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

發(fā)布緊急采購,3分鐘左右您將得到回復。