- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16586 > EVAL-ADN2850SDZ (Analog Devices Inc)BOARD EVAL FOR ADN2850SDZ PDF資料下載

參數(shù)資料

| 型號(hào): | EVAL-ADN2850SDZ |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 6/28頁 |

| 文件大?。?/td> | 0K |

| 描述: | BOARD EVAL FOR ADN2850SDZ |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 主要目的: | 數(shù)字電位器 |

| 嵌入式: | 否 |

| 已用 IC / 零件: | ADN2850 |

| 主要屬性: | 2 溝道,1024 位置 |

| 次要屬性: | SPI 接口 |

| 已供物品: | 板 |

第1頁第2頁第3頁第4頁第5頁當(dāng)前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

ADN2850

Data Sheet

Rev. E | Page 14 of 28

EEMEM PROTECTION

The write protect (

AA

WPEE

AA

) pin disables any changes to the

scratchpad register contents, except for the EEMEM setting,

which can still be restored using Instruction 1, Instruction 8,

and the

AA

PREE

AA

pulse. Therefore,

AA

WPEE

AA

can be used to provide a

hardware EEMEM protection feature.

DIGITAL INPUT AND OUTPUT CONFIGURATION

All digital inputs are ESD protected, high input impedance that

can be driven directly from most digital sources. Active at logic

low,

AA

PREE

AA

and

AA

WPEE

AA

must be tied to VDD, if they are not used. No

internal pull-up resistors are present on any digital input pins.

To avoid floating digital pins that might cause false triggering

in a noisy environment, add pull-up resistors. This is applicable

when the device is detached from the driving source when it is

programmed.

The SDO and RDY pins are open-drain digital outputs that only

need pull-up resistors if these functions are used. To optimize

the speed and power trade-off, use 2.2 k pull-up resistors.

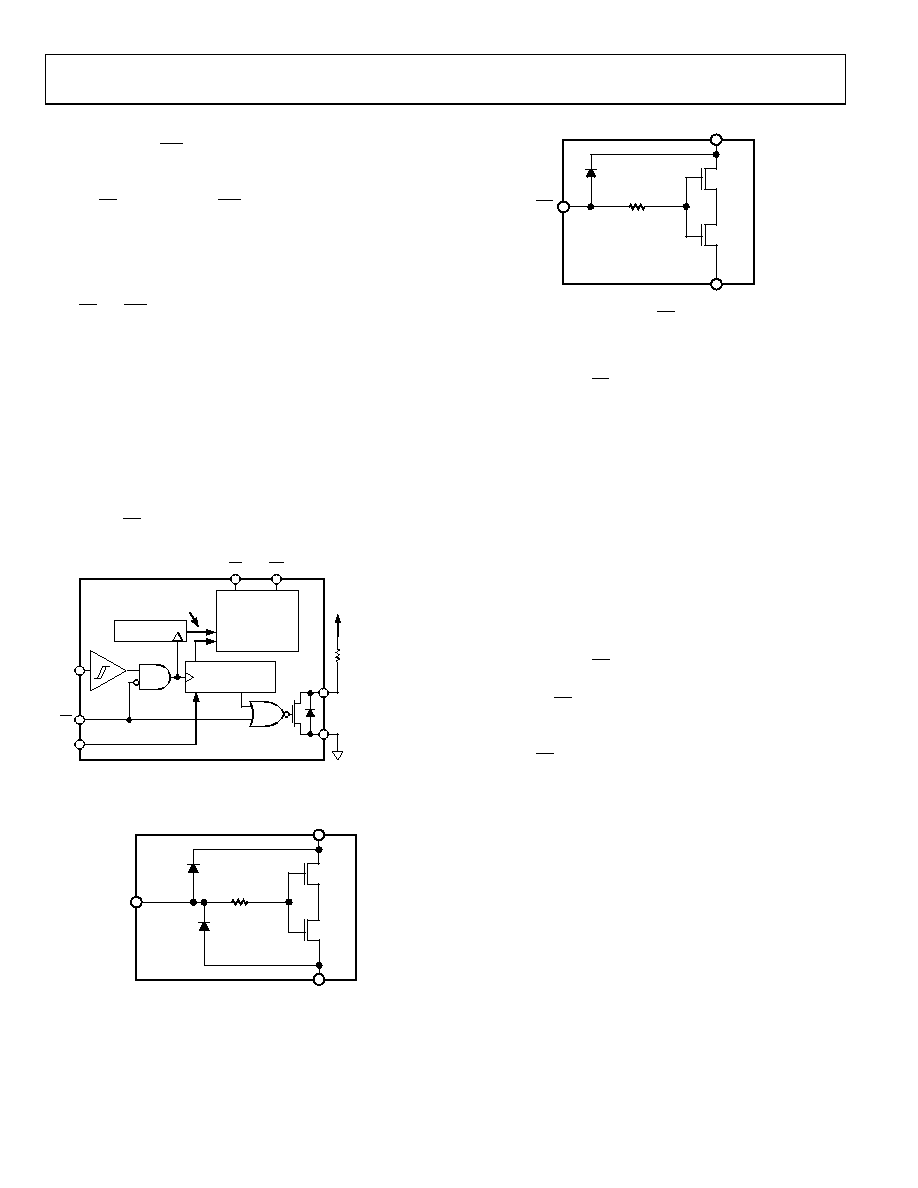

The equivalent serial data input and output logic is shown in

Figure 25. The open-drain output SDO is disabled whenever

chip-select (

AA

CSEE

AA

) is in logic high. ESD protection of the digital

inputs is shown in Figure 26 and Figure 27.

VALID

COMMAND

COUNTER

COMMAND

PROCESSOR

AND ADDRESS

DECODE

(FOR DAISY

CHAIN ONLY)

SERIAL

REGISTER

CLK

SDI

5V

RPULL-UP

SDO

GND

PR

WP

ADN2850

CS

0

2

6

0

-0

3

7

Figure 25. Equivalent Digital Input and Output Logic

LOGIC

PINS

VDD

GND

INPUTS

300

0

2

6

0

-0

3

8

Figure 26. Equivalent ESD Digital Input Protection

VDD

GND

INPUT

300

WP

0

2

6

0

-0

3

9

Figure 27. Equivalent

AA

WPEE

AA

Input Protection

SERIAL DATA INTERFACE

The ADN2850 contains a 4-wire SPI-compatible digital

interface (SDI, SDO,

AA

CSEE

AA

, and CLK). The 24-bit serial data-word

must be loaded with MSB first. The format of the word is shown in

Table 7. The command bits (C0 to C3) control the operation of the

digital resistor according to the command shown in Table 8. A0

to A3 are the address bits. A0 is used to address RDAC1 or RDAC2.

Address 2 to Address 14 are accessible by users for extra EEMEM.

Address 15 is reserved for factory usage. Table 10 provides an

address map of the EEMEM locations. D0 to D9 are the values

for the RDAC registers. D0 to D15 are the values for the EEMEM

registers.

The ADN2850 has an internal counter that counts a multiple of

24 bits (a frame) for proper operation. For example, ADN2850

works with a 24-bit or 48-bit word, but it cannot work properly

with a 23-bit or 25-bit word. To prevent data from mislocking

(due to noise, for example), the counter resets, if the count is not a

multiple of four when

AA

CSEE

AA

goes high but remains in the register if it

is multiple of four. In addition, the ADN2850 has a subtle

feature that, if

AA

CSEE

AA

is pulsed without CLK and SDI, the part

repeats the previous command (except during power-up). As a

result, care must be taken to ensure that no excessive noise exists in

the CLK or

AA

CSEE

AA

line that might alter the effective number-of-bits

pattern.

The SPI interface can be used in two slave modes: CPHA = 1,

CPOL = 1 and CPHA = 0, CPOL = 0. CPHA and CPOL refer to

the control bits that dictate SPI timing in the following

MicroConverters and microprocessors: ADuC812, ADuC824,

M68HC11, MC68HC16R1, and MC68HC916R1.

DAISY-CHAIN OPERATION

The serial data output pin (SDO) serves two purposes. It can be

used to read the contents of the wiper setting and EEMEM values

using Instruction 10 and Instruction 9, respectively. The remaining

instructions (Instruction 0 to Instruction 8, Instruction 11 to

Instruction 15) are valid for daisy-chaining multiple devices in

simultaneous operations. Daisy-chaining minimizes the number

of port pins required from the controlling IC (see Figure 28). The

SDO pin contains an open-drain N-Ch FET that requires a pull-up

resistor, if this function is used. As shown in Figure 28, users need

to tie the SDO pin of one package to the SDI pin of the next package.

Users may need to increase the clock period because the pull-up

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| V300B5E150BF2 | CONVERTER MOD DC/DC 5V 150W |

| EBM28DRYN | CONN EDGECARD 56POS DIP .156 SLD |

| 1-830638-5 | LGH-1L DBL MOLDED END LEAD |

| V300B48E150BL | CONVERTER MOD DC/DC 48V 150W |

| GSM12DRSD | CONN EDGECARD 24POS DIP .156 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EVAL-ADN2870 | 制造商:Analog Devices 功能描述:EVAL BOARD - Bulk |

| EVAL-ADN2871 | 制造商:Analog Devices 功能描述:EVAL KIT FOR 3.3V, 50 MBPS TO 4.25 GBPS,SGL-LOOP, LASER DIOD - Bulk |

| EVAL-ADN2890EB | 制造商:Analog Devices 功能描述:EVALUATION BOARD IC. - Bulk |

| EVAL-ADN2891EB | 制造商:Analog Devices 功能描述:EVAL KIT FOR 3.3V, 3.2 GBPS, LIMITING AMP - Bulk |

| EVAL-ADN2891EBZ | 制造商:Analog Devices 功能描述:HSN EVALUATION BOARD - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。