- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370260 > FW802A Low-Power PHY IEEE 1394A-2000 Two-Cable Transceiver/Arbiter Device PDF資料下載

參數(shù)資料

| 型號: | FW802A |

| 英文描述: | Low-Power PHY IEEE 1394A-2000 Two-Cable Transceiver/Arbiter Device |

| 中文描述: | 低功耗PHY的IEEE 1394A端口- 2000兩線收發(fā)器/仲裁器裝置 |

| 文件頁數(shù): | 16/36頁 |

| 文件大小: | 461K |

| 代理商: | FW802A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁

Intel

80200 Processor based on Intel

XScale

Microarchitecture

Package Information

16

August 2002

Datasheet

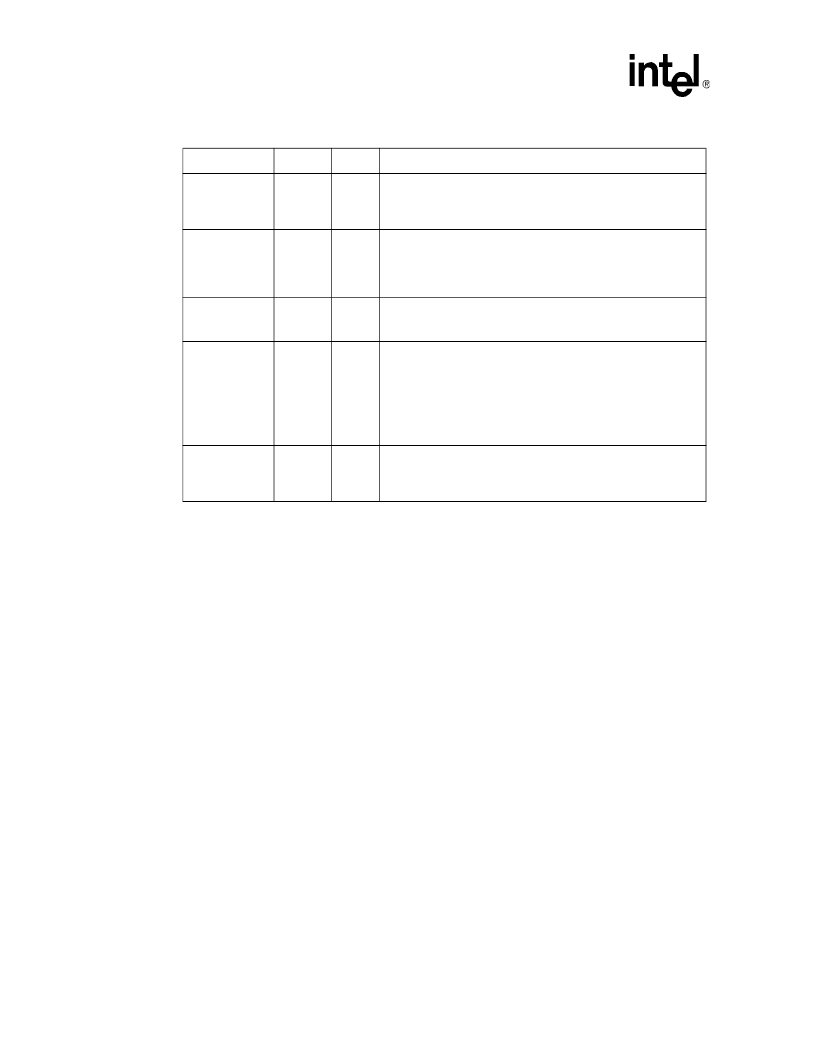

Table 5.

JTAG Pins

Name

Count

Type

Description

TCK

1

I

TEST CLOCK

is an input which provides the clocking function for

the IEEE 1149.1 Boundary Scan Testing (JTAG). State information

and data are clocked into the component on the rising edge and

data is clocked out of the component on the falling edge.

TDI

1

I

TEST DATA INPUT

is the serial input pin for the JTAG feature. TDI

is sampled on the rising edge of

TCK

, during the SHIFT-IR and

SHIFT-DR states of the Test Access Port. This signal has a weak

internal pullup to ensure proper operation when this signal is

unconnected.

TDO

1

O

TEST DATA OUTPUT

is the serial output pin for the JTAG feature.

TDO

is driven on the falling edge of

TCK

during the SHIFT-IR and

SHIFT-DR states of the Test Access Port. At other times,

TDO

floats.

TRST#

1

I

TEST RESET

asynchronously resets the Test Access Port (TAP)

controller function of IEEE 1149.1 Boundary Scan Testing (JTAG).

This signal has a weak internal pullup to ensure proper operation

when this signal is unconnected.

TRST#

must be driven low during processor reset to ensure proper

operation. Additionally, before performing JTAG test, the processor

should be reset and should have a valid clock at

CLK

to ensure it

does not enter a low-power mode.

TMS

1

I

TEST MODE SELECT

is sampled at the rising edge of

TCK

to

select the operation of the test logic for IEEE 1149.1 Boundary

Scan testing. This signal has a weak internal pullup to ensure

proper operation when this signal is unconnected.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FW802A-DB | Low-Power PHY IEEE 1394A-2000 Two-Cable Transceiver/Arbiter Device |

| FW802C | FW 802C LOW - POWER IEEE 1394A-2000 TWO CABLE TRANSCEIVER/ ARBITER DEVICE |

| FW802C-DB | FW 802C LOW - POWER IEEE 1394A-2000 TWO CABLE TRANSCEIVER/ ARBITER DEVICE |

| FW803-09-DB | PHY IEEE 1394A Three-Cable Transceiver/Arbiter Device |

| FW803 | PHY IEEE 1394A Three-Cable Transceiver/Arbiter Device |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FW802A-DB | 制造商:AGERE 制造商全稱:AGERE 功能描述:Low-Power PHY IEEE 1394A-2000 Two-Cable Transceiver/Arbiter Device |

| FW802B | 制造商:AGERE 制造商全稱:AGERE 功能描述:Low-Power PHY IEEE㈢ 1394A-2000 Two-Cable Transceiver/Arbiter Device |

| FW802B-DB | 制造商:Legerity 功能描述:DUAL LINE TRANSCEIVER, PQFP64 |

| FW802BF | 制造商:AGERE 制造商全稱:AGERE 功能描述:Low-Power PHY 1394a-2000 Two-Cable Transceiver/Arbiter Device |

| FW802BF-09-DB | 制造商:AGERE 制造商全稱:AGERE 功能描述:Low-Power PHY 1394a-2000 Two-Cable Transceiver/Arbiter Device |

發(fā)布緊急采購,3分鐘左右您將得到回復。