- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370686 > HS1-82C37ARH-Sample (Harris Corporation) Radiation Hardened CMOS High Performance Programmable DMA Controller PDF資料下載

參數(shù)資料

| 型號: | HS1-82C37ARH-Sample |

| 廠商: | Harris Corporation |

| 英文描述: | Radiation Hardened CMOS High Performance Programmable DMA Controller |

| 中文描述: | 輻射加固的CMOS高性能可編程DMA控制器 |

| 文件頁數(shù): | 4/28頁 |

| 文件大小: | 253K |

| 代理商: | HS1-82C37ARH-SAMPLE |

第1頁第2頁第3頁當前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

4

HS-82C37ARH

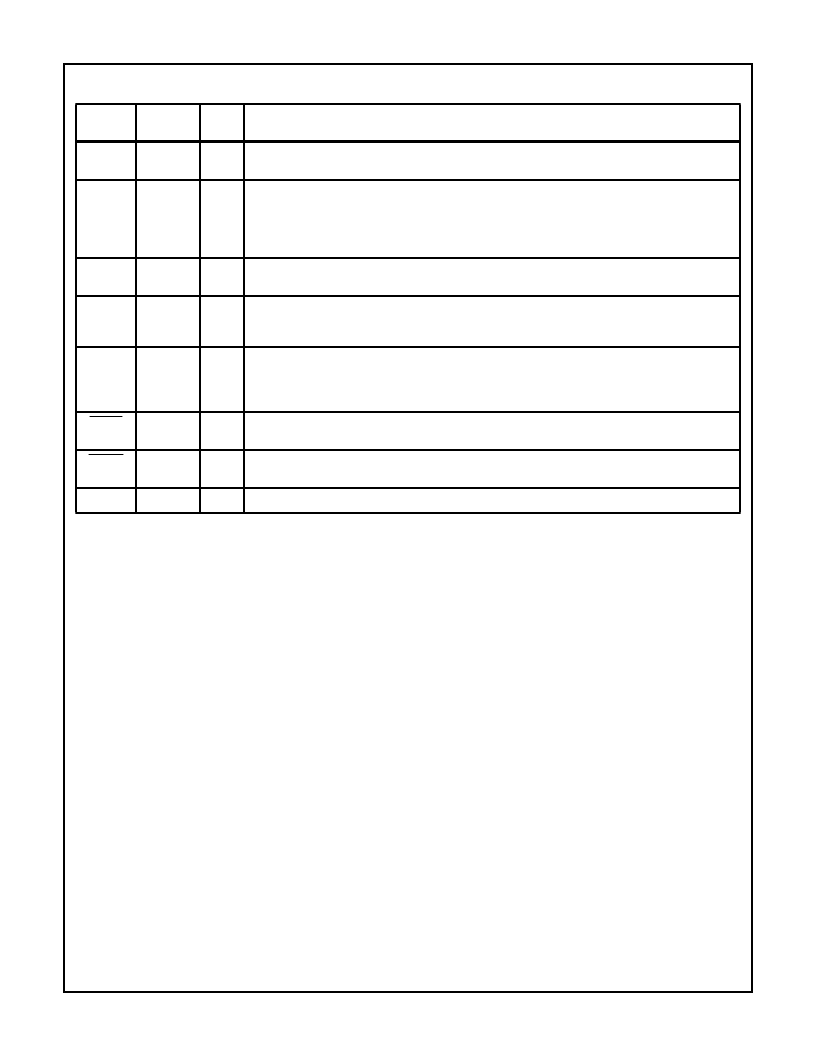

A4-A7

37-40

O

Address: The four most significant address lines are three-state outputs and provide 4 bits of address.

These lines are enabled only during the Active cycle.

HRQ

10

O

Hold Request: The Hold Request (HRQ) output is used to request control of the system bus. When a

DREQ occurs and the corresponding mask bit is clear, or a software DMA request is made, the HS-

82C37ARH issues HRQ. The HLDA signal then informs the controller when access to the system bus-

ses is permitted. For stand-alone operation where the HS-82C37ARH always controls the busses, HRQ

may be tied to HLDA. This will result in one S0 state before the transfer.

DACK0-

DACK3

14,15, 24,

25

O

DMA Acknowledge: DMA acknowledge is used to notify the individual peripherals when one has been

granted a DMA cycle. The sense of these lines is programmable. Reset initializes them to active low.

AEN

9

O

Address Enable: Address Enable enables the 8-bit latch containing the upper 8 address bits onto the

system address bus. AEN can also be used to disable other system bus drivers during DMA transfers.

AEN is active HIGH.

ADSTB

8

O

Address Strobe: This is an active high signal used to control latching of the upper address byte. It will

drive directly the strobe input of external transparent octal latches, such as the 82C82. During block op-

erations, ADSTB will only be issued when the upper address byte must be updated, thus speeding op-

eration through elimination of S1 states. (See Note 2).

MEMR

3

O

Memory Read: The Memory Read signal is an active low three-state output used to access data from

the selected memory location during a DMA Read or a Memory-to-Memory transfer.

MEMW

4

O

Memory Write: The Memory Write is an active low three-state output used to write data to the selected

memory location during a DMA Write or a Memory-to-Memory transfer.

NC

5

No connect. Pin 5 is open and should not be tested for continuity.

Pin Descriptions

(Continued)

SYMBOL

PIN

NUMBER

TYPE

DESCRIPTION

Spec Number

518058

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HS1-82C37ARH-Q | Radiation Hardened CMOS High Performance Programmable DMA Controller |

| HS-82C37 | Radiation Hardened CMOS High Performance Programmable DMA Controller |

| HS1-82C37ARH-8 | Radiation Hardened CMOS High Performance Programmable DMA Controller |

| HS9-82C37ARH-8 | Radiation Hardened CMOS High Performance Programmable DMA Controller |

| HS1-82C37ARH-Q | Radiation Hardened CMOS High Performance Programmable DMA Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HS1-82C52RH-8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:UART |

| HS1-82C54RH | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened CMOS Programmable Interval Timer |

| HS1-82C54RH/PROTO | 制造商:Intersil Corporation 功能描述:RAD HARD CMOS PROGRAMMABLE INTERVAL TIMER,PROTO,CLASS V - Rail/Tube |

| HS1-82C54RH-8 | 制造商:Intersil Corporation 功能描述:PROGRAMMABLE TIMER SGL 24PIN SBDIP - Rail/Tube |

| HS1-82C54RH-Q | 制造商:Intersil Corporation 功能描述:PROGRAMMABLE TIMER SGL 24PIN SBCDIP - Rail/Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復。