- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370781 > HYB18T1G400AFL-3S (INFINEON TECHNOLOGIES AG) 1 Gbit DDR2 SDRAM PDF資料下載

參數(shù)資料

| 型號(hào): | HYB18T1G400AFL-3S |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | 1 Gbit DDR2 SDRAM |

| 中文描述: | 1千兆位DDR2內(nèi)存 |

| 文件頁數(shù): | 77/89頁 |

| 文件大小: | 1752K |

| 代理商: | HYB18T1G400AFL-3S |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁當(dāng)前第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁

HYB18T1G400/800/160AF

1Gb DDR2 SDRAM

INFINEON Technologies

Page 77 Rev. 1.02 May 2004

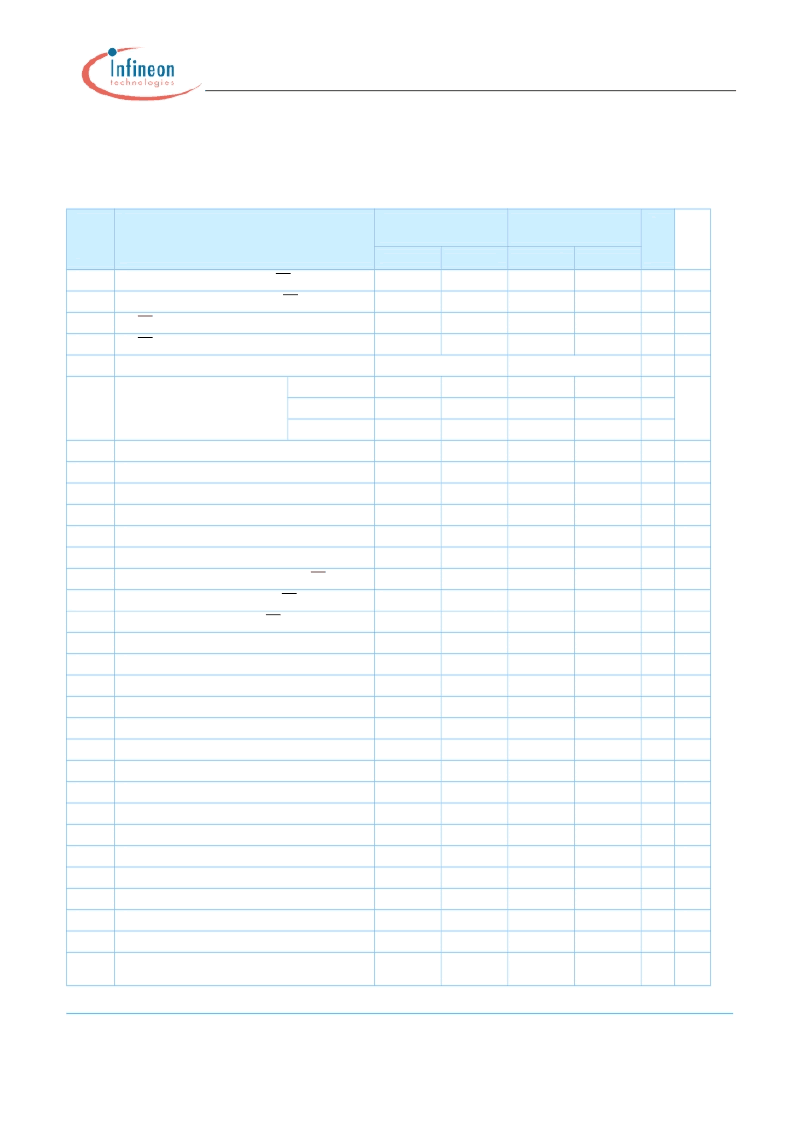

7.2 Timing Parameter by Speed Grade - DDR2-667

(VDDQ = 1.8V

±

0.1V; VDD = 1.8V

±

0.1V) (notes 1-4)

Symbol

Parameter

-3S

DDR2-667-555

-3

DDR2-667-444

Unit

Notes

min.

max

min.

max

tAC

DQ output access time from CK / CK

-450

+450

-450

+450

ps

tDQSCKDQS output access time from CK / CK

-400

+400

-400

+400

ps

tCH

CK, CK high-level width

0.45

0.55

0.45

0.55

tCK

tCL

CK, CK low-level width

0.45

0.55

0.45

0.55

tCK

tHP

Clock half period

min. (tCL, tCH)

min. (tCL, tCH)

5

tCK

Clock cycle time

CL = 3

5000

8000

5000

8000

ps

6

CL = 4

5000

8000

3000

8000

ps

CL = 5

3000

8000

3000

8000

ps

tIS

Address and control input setup time

150

-

150

-

ps

7

tIH

Address and control input hold time

275

-

275

-

ps

7

tDS

DQ and DM input setup time

50

-

50

-

ps

8

tDH

DQ and DM input hold time

175

-

175

-

ps

8

tIPW

Address and control input pulse width (each input)

0.6

-

0.6

-

tCK

tDIPW

DQ and DM input pulse width (each input)

0.35

-

0.35

-

tCK

tHZ

Data-out high-impedance time from CK / CK

-

tACmax

-

tACmax

ps

9

tLZ

(DQ)

DQ low-impedance time from CK / CK

2*tACmin

tACmax

2*tACmin

tACmax

ps

9

tLZ

(DQS)

DQS low-impedance from CK / CK

tACmin

tACmax

tACmin

tACmax

ps

9

tDQSQ

DQS-DQ skew (for DQS & associated DQ signals)

-

250

-

250

ps

18

tQHS

Data hold skew factor

-

350

-

350

ps

tQH

Data output hold time from DQS

tHP-tQHS

tHP-tQHS

tDQSS

Write command to 1st DQS latching transition

WL-0.25

WL+0.25

WL-0.25

WL+0.25

tCK

tDQSL,HDQS input low (high) pulse width (write cycle)

0.35

-

0.35

-

tCK

tDSS

DQS falling edge to CK setup time (write cycle)

0.2

-

0.2

-

tCK

tDSH

DQS falling edge hold time from CK (write cycle)

0.2

-

0.2

-

tCK

tMRD

Mode register set command cycle time

2

-

2

-

tCK

tWPRE

Write preamble

0.35

-

0.35

-

tCK

tWPST

Write postamble

0.40

0.60

0.40

0.60

tCK

10

tRPRE

Read preamble

0.9

1.1

0.9

1.1

tCK

9

tRPST

Read postamble

0.40

0.60

0.40

0.60

tCK

9

tRAS

Active to Precharge command

45

70000

45

70000

ns

11

tRC

Active to Active/Auto-Refresh command period

60

-

57

-

ns

tRFC

Auto-Refresh to Active/Auto-Refresh command period

127.5

-

127.5

-

ns

12

tRCD

Active to Read or Write delay

(with and without Auto-Precharge)

15

-

12

-

ns

13

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYB18T1G160AFL-3S | 1 Gbit DDR2 SDRAM |

| HYB18T1G400AFL-5 | 1 Gbit DDR2 SDRAM |

| HYB18T1G800AF-3 | 1 Gbit DDR2 SDRAM |

| HYB18T1G800AF-37 | 1 Gbit DDR2 SDRAM |

| HYB18T1G800AF-3S | POT 1.0K OHM 1/4 SQ CERM SL ST |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYB18T1G800BF-3S | 功能描述:IC DDR2 SDRAM 1GBIT 68TFBGA RoHS:是 類別:集成電路 (IC) >> 存儲(chǔ)器 系列:- 標(biāo)準(zhǔn)包裝:60 系列:- 格式 - 存儲(chǔ)器:EEPROMs - 串行 存儲(chǔ)器類型:EEPROM 存儲(chǔ)容量:16K (2K x 8) 速度:2MHz 接口:SPI 3 線串行 電源電壓:2.5 V ~ 5.5 V 工作溫度:-40°C ~ 85°C 封裝/外殼:8-DIP(0.300",7.62mm) 供應(yīng)商設(shè)備封裝:8-PDIP 包裝:管件 產(chǎn)品目錄頁面:1449 (CN2011-ZH PDF) |

| HYB18T256400AF-3.7 | 制造商:Infineon Technologies AG 功能描述:64M X 4 DDR DRAM, 0.5 ns, PBGA60 |

| HYB18T256400AF-5 | 制造商:Infineon Technologies AG 功能描述:SDRAM, DDR, 64M x 4, 60 Pin, Plastic, BGA |

| HYB18T256800AF-5 | 制造商:Infineon Technologies AG 功能描述: |

| HYB18T512161BF-25 | 制造商:Qimonda 功能描述:SDRAM, DDR, 32M x 16, 84 Pin, Plastic, BGA |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。