- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370794 > HYB514800BJ-60 (SIEMENS A G) 512kx8-Bit Dynamic RAM PDF資料下載

參數(shù)資料

| 型號: | HYB514800BJ-60 |

| 廠商: | SIEMENS A G |

| 元件分類: | DRAM |

| 英文描述: | 512kx8-Bit Dynamic RAM |

| 中文描述: | 512K X 8 FAST PAGE DRAM, 60 ns, PDSO28 |

| 文件頁數(shù): | 8/22頁 |

| 文件大小: | 211K |

| 代理商: | HYB514800BJ-60 |

Semiconductor Group

132

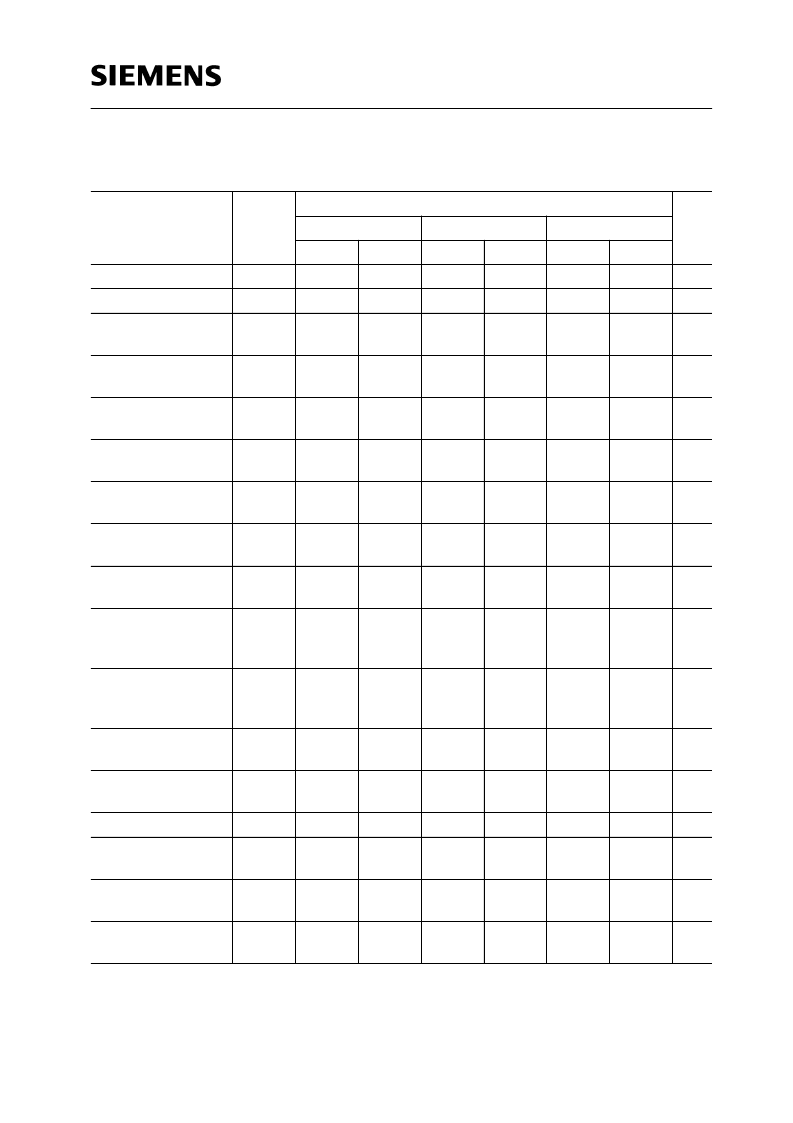

Data hold time

9)

t

DH

t

REF

t

WCS

15

–

15

–

15

–

ns

Refresh period

–

16

–

16

–

16

ms

Write command

setup time

10)

0

–

0

–

0

–

ns

CAS to WRITE delay

time

10)

t

CWD

50

–

50

–

50

–

ns

RAS to WRITE delay

time

10)

t

RWD

90

–

100

–

110

–

ns

Column address to

WRITE delay time

10)

t

AWD

60

–

65

–

70

–

ns

CAS setup time (CBR

cycle)

t

CSR

5

–

5

–

5

–

ns

CAS hold time (CBR

cycle)

t

CHR

15

–

15

–

15

–

ns

RAS to CAS

precharge time

t

RPC

0

–

0

–

0

–

ns

CAS precharge time

(CAS before RAS

counter test cycle)

t

CPT

30

–

40

–

40

–

ns

Write to RAS

precharge time

(CBR cycle)

t

WRP

10

–

10

–

10

–

ns

Write to RAS hold

time (CBR cycle)

t

WRH

10

–

10

–

10

–

ns

OE command hold

time

t

OEH

20

–

20

–

20

–

ns

OE acces time

t

OEA

t

ROH

–

20

–

20

–

20

ns

RAS hold time

referenced to OE

10

–

10

–

10

–

ns

Output buffer turn-off

delay from OE

t

OEZ

0

20

0

20

0

20

ns

Data to CAS low

delay

14)

t

DZC

0

–

0

–

0

–

ns

AC Characteristics

(cont’d)

4)

T

A

= 0 to 70 C;

V

CC

= 5 V

±

10 %;

t

T

= 5 ns

Parameter

Symbol

Limit Values

Unit

-60

-70

-80

min.

max.

min.

max.

min.

max.

HYB 514800BJ -60/-70/-80

512k x 8 DRAM

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYBRID-1998 | |

| HYBRID-CAPABILITIES | Optoelectronic |

| HYBRID-CUSTOM | ASIC |

| HYC9088AR-LF | ARCNET Twisted Pair and Coaxial Compatible High Impedance Transceiver HIT |

| HYC9088A | ARCNET TWISTED PAIR AND COAXIAL COMPLATIBLE HIGH IMPEDANCE TRANSCEIVER HIT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYB514800BJ-70 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:512kx8-Bit Dynamic RAM |

| HYB514800BJ-80 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:512kx8-Bit Dynamic RAM |

| HYB514800BJL-60 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 Fast Page Mode DRAM |

| HYB514800BJL-70 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 Fast Page Mode DRAM |

| HYB514800BJL-80 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 Fast Page Mode DRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。