- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360744 > ICS1889 100Base-FX Integrated PHYceiverTM PDF資料下載

參數(shù)資料

| 型號: | ICS1889 |

| 英文描述: | 100Base-FX Integrated PHYceiverTM |

| 中文描述: | 100Base - FX光纖綜合PHYceiverTM |

| 文件頁數(shù): | 8/35頁 |

| 文件大小: | 1096K |

| 代理商: | ICS1889 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

8

ICS1889

Control Register (register 0)

The control register is a 16-bit read/write register used to set

the basic configuration modes of the

ICS1889

. It is accessed

through the management interface of the MII.

Reset (bit 15) default = 0

Setting this bit to a logic 1 will result in the

ICS1889

setting

all its status and control registers to their default values.

During this process the

ICS1889

may change internal states

and the states of physical links attached to it. While in process,

the bit will remain set and no other write commands to the

control register will be accepted. The reset process will be

completed within 500ms and the bit will be cleared indicating

that the reset process is complete.

Loop Back (bit 14)

Setting this bit to a logic one causes the

ICS1889

to tristate

the transmit circuitry from sending data and the receive

circuitry from receiving data. The collision detection circuitry

is also disabled unless the collision test command bit is set.

Data presented to the MII transmit data path is returned to the

MII receive data path (see

ICS1889

Block Diagram, page 2).

Data Rate (bit 13)

This bit is permanently set to a logic one indicating that only

the 100 Mbps mode is supported.

Auto-Negotiation Enable (bit 12)

This feature is not available with fiber optic solutions. This bit

is permanently set to a logic zero indicating that it is not

supported.

Power-Down (bit 11)

Setting it to logic one will cause the

ICS1889

to isolate its

transmit data output and its MII interface with the exception

of the management interface. The

ICS1889

will then enter a

power-down mode where only the management interface and

logic remain active. Setting this bit to logic zero after it has

been set to a logic one will cause the

ICS1889

to power-up its

logic and then reset all error conditions. It then enables

transmit data and the MII interface. This process takes 500ms

to complete.

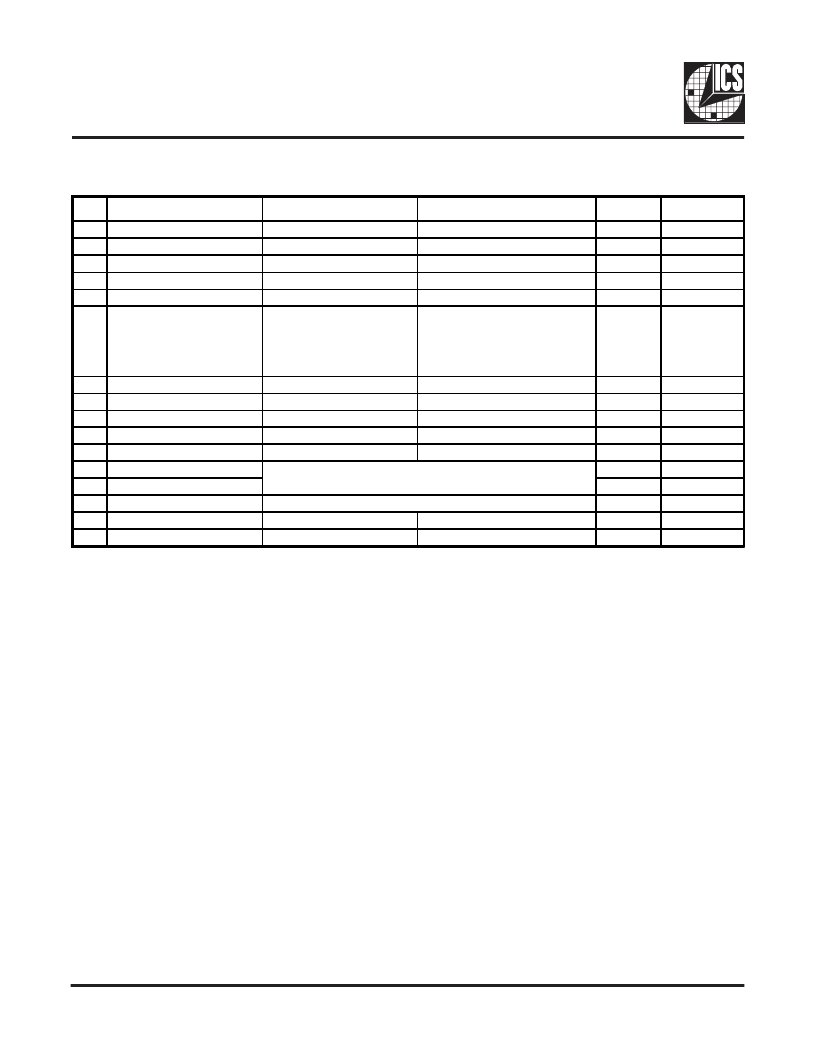

Control Register (register 0)

BIT

15

14

13

12

11

10

Function

Effect when bit = 0

No Effect

Disable loop back mode

Always set to a logic one 100 Mpbs operation

No Effect

Normal Mode

No Effect

Effect when bit = 1

Reset PHY

Enable loop back mode

Access

RW/SC

RW

RO

RO

RW

RW

Default

0

0

1

0

0

0 if PHY

Address

< >0,

1 if PHY

Address=0

0

0

0

0

0

0

0

0

0

0

Reset

Loop Back

Data Rate

Auto-Negotiate Enable

Power-Down

Isolate

Always set to logic zero

Reduced

power consumption

Isolate PHY from MII

9

8

7

6

5

4

3

2

1

0

Restart Auto-Negotitation No Effect

Duplex Mode

Collision Test

Reserved

Reserved

Reserved

Always set to logic zero

Full Duplex

Enable collision signal test

RO

RW

RW

RO

RO

RO

RO

RO

RO

RO

Half Duplex

No Effect

If read, bits 0-6 and bits 9 and 12 will return logic

zeroes and bit 13 will return a logic one.

Writes to these bits will have no effect.

Reserved

Reserved

Reserved

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ICS1892 | 10Base-T/100Base-TX Integrated PHYceiver |

| ICS1892Y | 10Base-T/100Base-TX Integrated PHYceiver |

| ICS1892Y-10 | 10Base-T/100Base-TX Integrated PHYceiver |

| ICS1892Y-14 | 10Base-T/100Base-TX Integrated PHYceiver |

| ICS1893AF | 3.3V 10Base-T/100Base-TX Integrated PHYceiverTM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ICS1890 | 制造商:ICS 制造商全稱:ICS 功能描述:Auto-Negotiation Advertisement Register (register 4 [0x04]) |

| ICS1890Y | 制造商:ICS 功能描述: 制造商:ICS 功能描述:LAN Transceiver, Single, 64 Pin, Plastic, QFP 制造商:ICS 功能描述:1890Y-4 制造商:Integrated Device Technology Inc 功能描述:LAN Transceiver, Single, 64 Pin, Plastic, QFP |

| ICS1890Y-14 | 制造商:ICS 制造商全稱:ICS 功能描述:Auto-Negotiation Advertisement Register (register 4 [0x04]) |

| ICS1890Y-4 | 制造商:ICS 功能描述:1890Y-4 |

| ICS1891 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN Transceiver |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。