- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360788 > ICSSSTUBF32866Az(LF)T 25-Bit Configurable Registered Buffer for DDR2 PDF資料下載

參數(shù)資料

| 型號(hào): | ICSSSTUBF32866Az(LF)T |

| 英文描述: | 25-Bit Configurable Registered Buffer for DDR2 |

| 中文描述: | 25位可配置的注冊(cè)緩沖DDR2內(nèi)存 |

| 文件頁(yè)數(shù): | 22/28頁(yè) |

| 文件大小: | 308K |

| 代理商: | ICSSSTUBF32866AZ(LF)T |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)當(dāng)前第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)

22

ICSSSTUBF32866A

Advance Information

1240—07/17/06

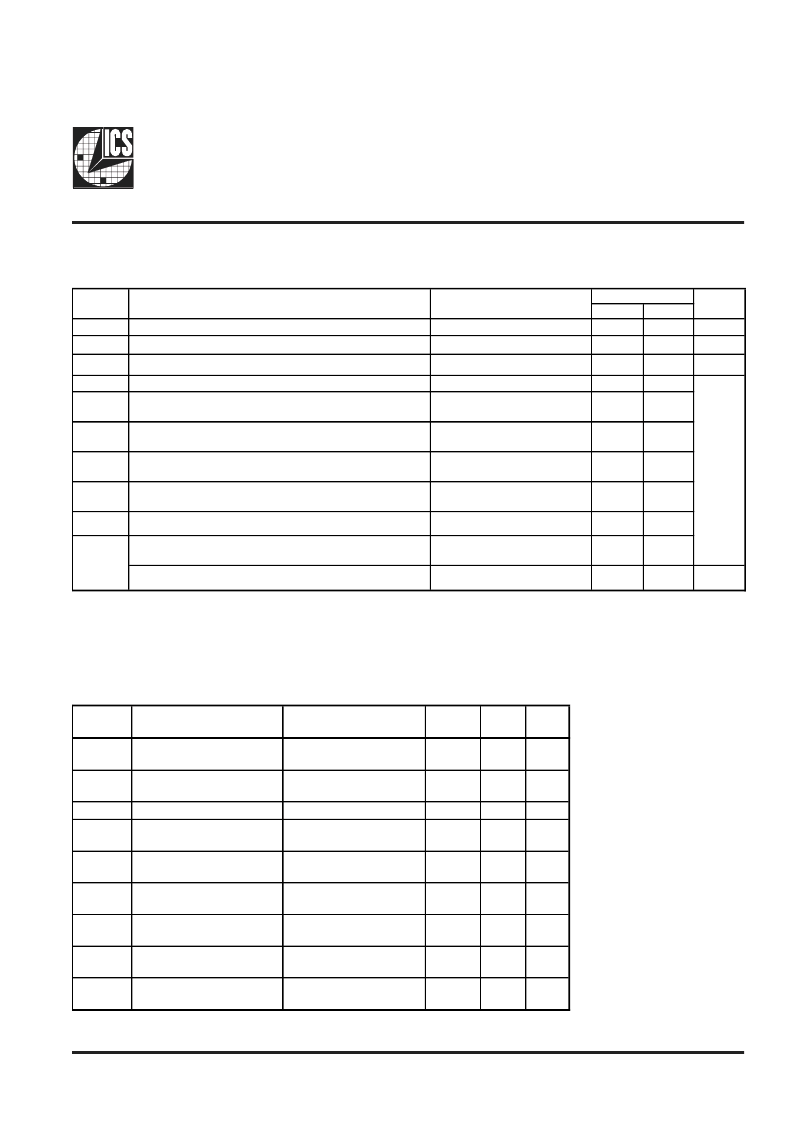

Timing Requirements

(over recommended operating free-air temperature range, unless otherwise noted)

MIN

-

1

MAX

410

-

f

clock

t

W

t

ACT

t

INACT

Clock frequency

Pulse duration, CK, CK HIGH or LOW

MHz

ns

Differential inputs active time (See Notes 1 and 2)

-

10

ns

Differential inputs inactive time (See Notes 1 and 3)

-

15

ns

t

su

Setup time

DCS# before CK

↑

, CK#

↓

,

CSR# high

CSR# before CK

↑

, CK#

↓

,

DCS# high

DCS# before CK

↑

, CK#

↓

,

CSR# low

DODT, DCKE and data before

CK

↑

, CK#

↓

PAR_IN before CK

↑

, CK#

↓

DCS#, DODT, DCKE and Q

after CK

↑

, CK#

↓

PAR_IN after CK

↑

, CK#

↓

0.55

ns

t

su

Setup time

0.55

ns

t

su

Setup time

0.35

ns

t

su

Setup time

0.35

ns

t

su

Setup time

0.35

ns

Hold time

0.35

ns

Hold time

1 - Guaranteed by design, not 100% tested in production.

2 - For data signal input slew rate of 1V/ns.

3 - For data signal input slew rate of 0.5V/ns and < 1V/ns.

0.35

ns

4 - CLK/CLK# signal input slew rate of 1V/ns.

SYMBOL

Notes:

t

H

V

DD

= 1.8V ±0.1V

UNITS

PARAMETERS

Switching Characteristics

(over recommended operating free-air temperature range, unless otherwise noted)

Symbol

Parameter

Measurement

Conditions

MIN

MAX

Units

fmax

Max input clock frequency

410

MHz

t

PDM

Propagation delay, single

bit switching

Propagation delay

Low to High propagation

delay

High to low propagation

delay

Propagation delay

simultaneous switching

High to low propagation

delay

High to low propagation

delay

Low to High propagation

delay

2. Guaranteed by design, not 100% tested in production.

CK

↑

to CK#

↓

QN

1.1

1.5

ns

t

PD

CK

↑

to CK#

↓

to PPO

0.5

1.7

ns

t

LH

CK

↑

to CK#

↓

to QERR#

1.2

3

ns

t

HL

CK

↑

to CK#

↓

to QERR#

1

2.4

ns

t

PDMSS

CK

↑

to CK#

↓

QN

-

1.6

ns

t

PHL

Rst#

↓

to QN

↓

3

ns

t

PHL

Rst#

↓

to PPO

↓

3

ns

t

PLH

Rst#

↓

to QERR#

↑

3

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ICSSSTUF32864A | 25-Bit Configurable Registered Buffer for DDR2 |

| ICSSSTUF32864AYHLF-T | 25-Bit Configurable Registered Buffer for DDR2 |

| ICSSSTV16857CG-T | DDR 14-Bit Registered Buffer |

| ICSSSTV16857yG-T | DDR 14-Bit Registered Buffer |

| ICSSSTV16859CG-T | DDR 13-Bit to 26-Bit Registered Buffer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ICSSSTUF32864A | 制造商:ICS 制造商全稱:ICS 功能描述:25-Bit Configurable Registered Buffer for DDR2 |

| ICSSSTUF32864AYHLF-T | 制造商:ICS 制造商全稱:ICS 功能描述:25-Bit Configurable Registered Buffer for DDR2 |

| ICSSSTV16857 | 制造商:ICS 制造商全稱:ICS 功能描述:DDR 14-Bit Registered Buffer |

| ICSSSTV16857CG-T | 制造商:ICS 制造商全稱:ICS 功能描述:DDR 14-Bit Registered Buffer |

| ICSSSTV16857YG-T | 制造商:ICS 制造商全稱:ICS 功能描述:DDR 14-Bit Registered Buffer |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。