- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360788 > ICSSSTUBF32866Az(LF)T 25-Bit Configurable Registered Buffer for DDR2 PDF資料下載

參數(shù)資料

| 型號: | ICSSSTUBF32866Az(LF)T |

| 英文描述: | 25-Bit Configurable Registered Buffer for DDR2 |

| 中文描述: | 25位可配置的注冊緩沖DDR2內(nèi)存 |

| 文件頁數(shù): | 26/28頁 |

| 文件大小: | 308K |

| 代理商: | ICSSSTUBF32866AZ(LF)T |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當前第26頁第27頁第28頁

26

ICSSSTUBF32866A

Advance Information

1240—07/17/06

Test circuits and switching waveforms (cont’d)

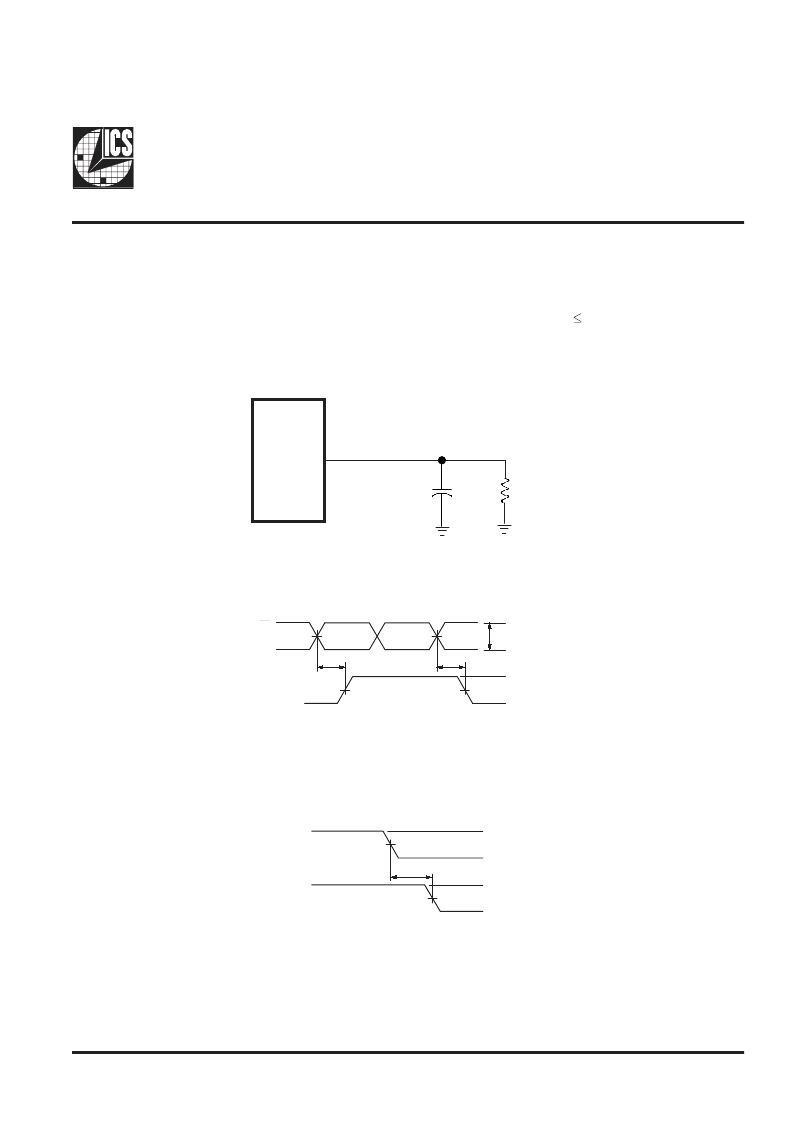

3.4 Partial-parity-out load circuit and voltage measurement information (V

DD

= 1.8 V ± 0.1 V)

All input pulses are supplied by generators having the following characteristics: PRR

Z

o

= 50

input slew rate = 1 V/ns ± 20%, unless otherwise specified.

10 MHz;

(1) C

L

includes probe and jig capacitance.

Figure 32 — Partial-parity-out load circuit,

V

TT

= V

DD

/2

t

PLH

an t

PHL

are the same as t

PD

.

V

I(PP)

= 600 mV

Figure 33 — Partial-parity-out voltage waveforms; propagation delay times with respect to clock inputs

V

TT

= V

DD

/2

t

PLH

an t

PHL

are the same as t

PD

.

V

IH

= V

REF

+ 250 mV (AC voltage levels for differential inputs. V

IH

= V

DD

for LVCMOS inputs.

V

IL

= V

REF

- 250 mV (AC voltage levels) for differential inputs. V

IL

= V

DD

for LVCMOS inputs.

Figure 34 — Partial-parity-out voltage waveforms; propagation delay times with respect to reset input

VOH

VOL

OUTPUT

tPLH

002aaa375

VTT

VICR

VICR

tPHL

CK

CK

Vi(p-p)

tPHL

002aaa376

LVCMOS RST#

INPUT

OUTPUT

VTT

VDD/2

VIH

VIL

VOH

VOL

DUT

Out

Test Point

RL=

CL =

5 pF

(see Note A)

1 k

相關PDF資料 |

PDF描述 |

|---|---|

| ICSSSTUF32864A | 25-Bit Configurable Registered Buffer for DDR2 |

| ICSSSTUF32864AYHLF-T | 25-Bit Configurable Registered Buffer for DDR2 |

| ICSSSTV16857CG-T | DDR 14-Bit Registered Buffer |

| ICSSSTV16857yG-T | DDR 14-Bit Registered Buffer |

| ICSSSTV16859CG-T | DDR 13-Bit to 26-Bit Registered Buffer |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ICSSSTUF32864A | 制造商:ICS 制造商全稱:ICS 功能描述:25-Bit Configurable Registered Buffer for DDR2 |

| ICSSSTUF32864AYHLF-T | 制造商:ICS 制造商全稱:ICS 功能描述:25-Bit Configurable Registered Buffer for DDR2 |

| ICSSSTV16857 | 制造商:ICS 制造商全稱:ICS 功能描述:DDR 14-Bit Registered Buffer |

| ICSSSTV16857CG-T | 制造商:ICS 制造商全稱:ICS 功能描述:DDR 14-Bit Registered Buffer |

| ICSSSTV16857YG-T | 制造商:ICS 制造商全稱:ICS 功能描述:DDR 14-Bit Registered Buffer |

發(fā)布緊急采購,3分鐘左右您將得到回復。