- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄10007 > IDT72V3614L20PQF (IDT, Integrated Device Technology Inc)IC FIFO 64X36X2 20NS 132QFP PDF資料下載

參數(shù)資料

| 型號: | IDT72V3614L20PQF |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數(shù): | 30/32頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FIFO 64X36X2 20NS 132QFP |

| 標(biāo)準(zhǔn)包裝: | 36 |

| 系列: | 72V |

| 功能: | 異步,同步 |

| 存儲(chǔ)容量: | 4.6K(64 x 36 x2) |

| 數(shù)據(jù)速率: | 50MHz |

| 訪問時(shí)間: | 20ns |

| 電源電壓: | 3 V ~ 3.6 V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 132-BQFP 緩沖式 |

| 供應(yīng)商設(shè)備封裝: | 132-PQFP(24.13x24.13) |

| 包裝: | 托盤 |

| 其它名稱: | 72V3614L20PQF |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當(dāng)前第30頁第31頁第32頁

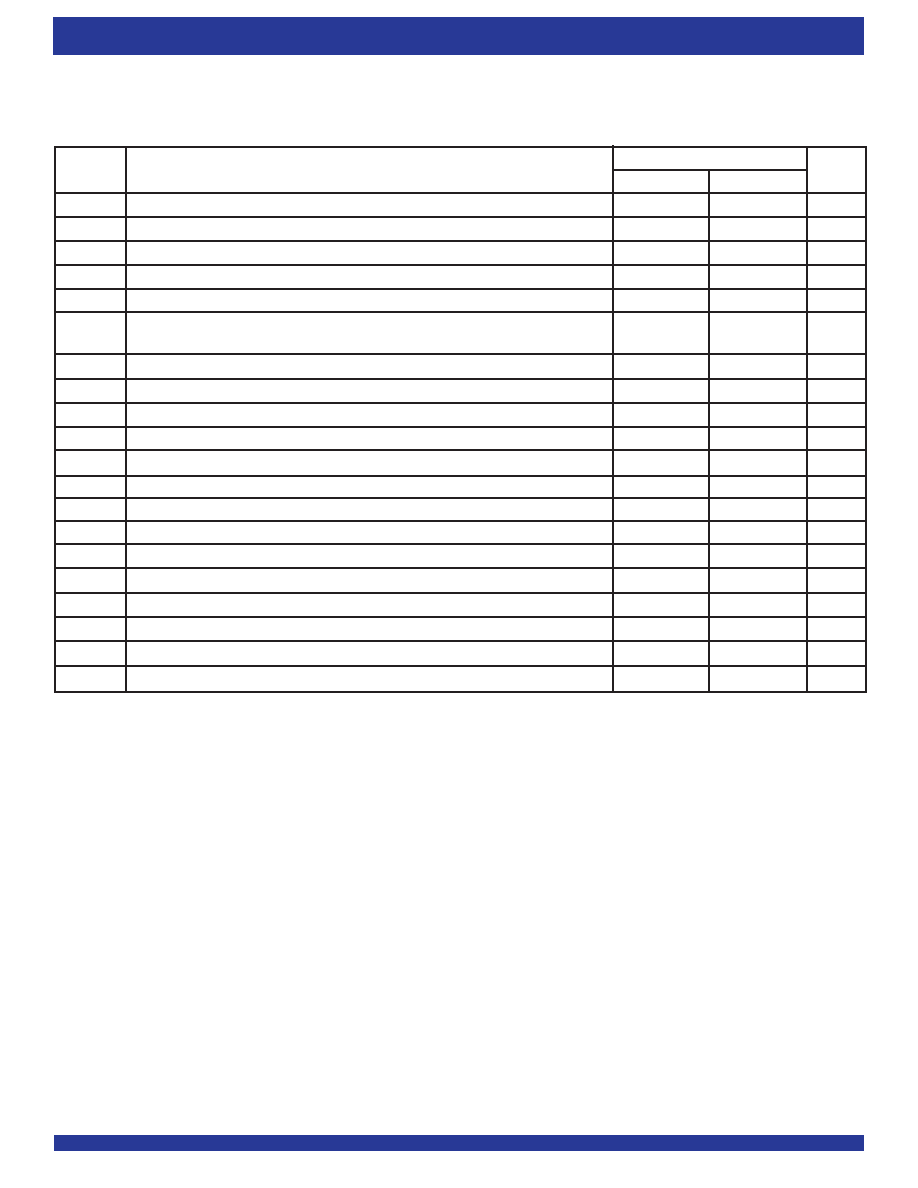

IDT72V3614 3.3V, CMOS SyncBiFIFOTM WITH

BUS-MATCHING AND BYTE SWAPPING 64 x 36 x 2

COMMERCIALTEMPERATURERANGE

7

DC ELECTRICAL CHARACTERISTICS OVER RECOMMENDED RANGES OF

SUPPLY VOLTAGE AND OPERATING FREE-AIR TEMPERATURE

tSKEW2(3,4)

Skew Time, between CLKA

↑ and CLKB↑ for AEA, AEB,

14

–

14

–

16

–

ns

AFA, and AFB

NOTES:

1. Only applies for a clock edge that does a FIFO read.

2. Requirement to count the clock edge as one of at least four needed to reset a FIFO.

3. Skew time is not a timing constraint for proper device operation and is only included to illustrate the timing relationship between CLKA cycle and CLKB cycle.

4. Design simulated, not tested.

Commercial: Vcc=3.3V± 0.30V; TA = 0

°C to +70°C; JEDEC JESD8-A compliant

IDT72V3614L15

Symbol

Parameter

Min.

Max.

Unit

fS

Clock Frequency, CLKA or CLKB

–

66.7

Mhz

tCLK

Clock Cycle Time, CLKA or CLKB

15

–

ns

tCLKH

Pulse Duration, CLKA or CLKB HIGH

6

–

ns

tCLKL

Pulse Duration, CLKA or CLKB LOW

6

–

ns

tDS

Setup Time, A0-A35 before CLKA

↑ and B0-B35 before CLKB↑

4–

ns

tENS

Setup Time, CSA, W/RA, ENA and MBA before CLKA

↑; CSB,W/RB and

5

–

ns

ENB before CLKB

↑

tSZS

Setup Time, SIZ0, SIZ1,and BE before CLKB

↑

4–

ns

tSWS

Setup Time, SW0 and SW1 before CLKB

↑

6–

ns

tPGS

Setup Time, ODD/EVEN and PGA before CLKA

↑; ODD/EVEN and PGB before CLKB↑(1)

4–

ns

tRSTS

Setup Time, RST LOW before CLKA

↑ or CLKB↑(2)

5–

ns

tFSS

Setup Time, FS0 and FS1 before RST HIGH

5

–

ns

tDH

Hold Time, A0-A35 after CLKA

↑ and B0-B35 after CLKB↑

1–

ns

tENH

Hold Time, CSA, W/RA, ENA and MBA after CLKA

↑; CSB, W/RB and ENB after CLKB↑

1–

ns

tSZH

Hold Time, SIZ0, SIZ1, and BE after CLKB

↑

1–

ns

tSWH

Hold Time, SW0 and SW1 after CLKB

↑

1–

ns

tPGH

Hold Time, ODD/EVEN and PGA after CLKA

↑; ODD/EVEN and PGB after CLKB↑(1)

0–

ns

tRSTH

Hold Time, RST LOW after CLKA

↑ or CLKB↑(2)

5–

ns

tFSH

Hold Time, FS0 and FS1 after RST HIGH

4

–

ns

tSKEW1(3)

Skew Time, between CLKA

↑ and CLKB↑ for EFA, EFB, FFA, FFB

8–

ns

tSKEW2(3,4)

Skew Time, between CLKA

↑ and CLKB↑ for AEA, AEB, AFA, and AFB

14

–

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT72V3613L20PQF | IC FIFO CLOCK 64X36 20NS 132PQFP |

| VI-261-IW-F3 | CONVERTER MOD DC/DC 12V 100W |

| XRT82D20IWTR-F | IC LIU E1 SGL 28SOJ |

| VE-BNR-MX-B1 | CONVERTER MOD DC/DC 7.5V 75W |

| MS27499E12A3SB | CONN RCPT 3POS BOX MNT W/SCKT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72V3622L10PF | 功能描述:IC BIFIFO 256X36X2 10NS 120-TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72V3622L10PF8 | 功能描述:IC BIFIFO 256X36X2 10NS 120-TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72V3622L10PFG | 制造商:Integrated Device Technology Inc 功能描述:IC BIFIFO 256X36X2 10NS 120-TQFP |

| IDT72V3622L10PFG8 | 制造商:Integrated Device Technology Inc 功能描述:IC BIFIFO 256X36X2 10NS 120-TQFP |

| IDT72V3622L10PQF | 功能描述:IC BIFIFO 256X36X2 10NS 132-PQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。