- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377484 > IDT77V1254L25L25PG (Integrated Device Technology, Inc.) Quad Port PHY (Physical Layer) for 25.6 and 51.2 ATM Networks PDF資料下載

參數(shù)資料

| 型號: | IDT77V1254L25L25PG |

| 廠商: | Integrated Device Technology, Inc. |

| 英文描述: | Quad Port PHY (Physical Layer) for 25.6 and 51.2 ATM Networks |

| 中文描述: | 四端口PHY(實(shí)體層)為25.6和51.2 ATM網(wǎng)絡(luò) |

| 文件頁數(shù): | 23/47頁 |

| 文件大小: | 840K |

| 代理商: | IDT77V1254L25L25PG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當(dāng)前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁

23 of 47

September 21, 2001

IDT77V1254L25

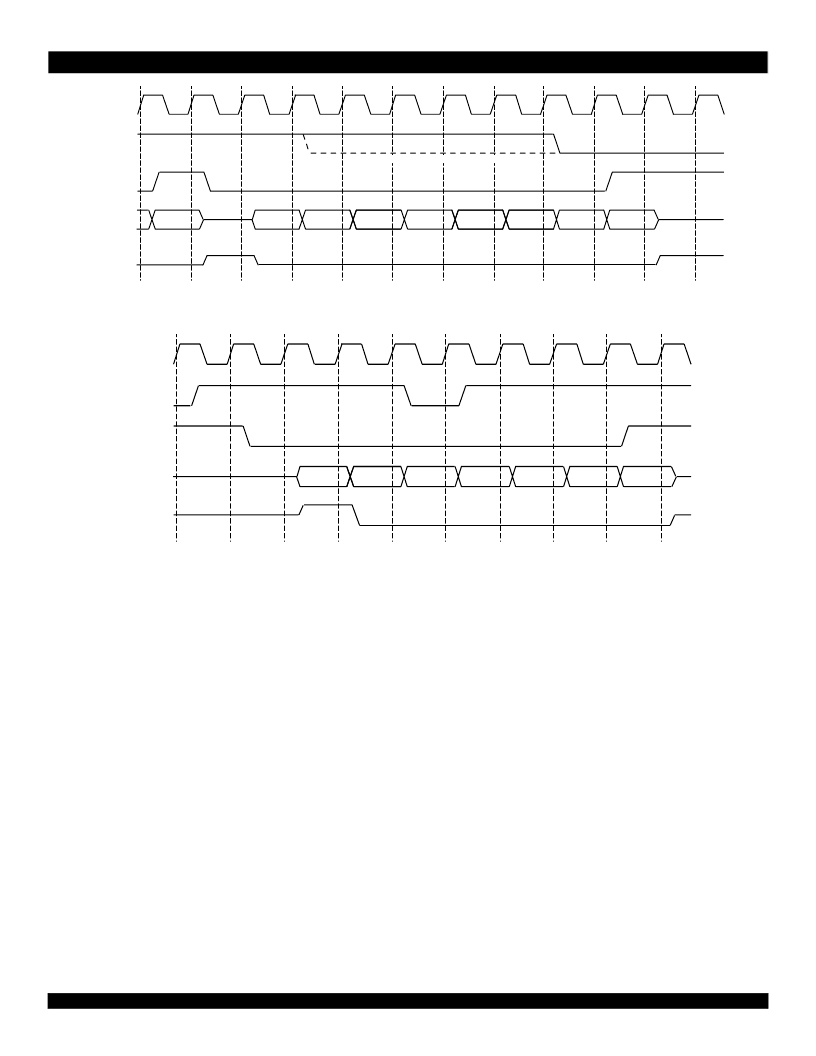

Figure 20 Utopia 1 Receive Handshake - RXCLAV Deassertion

Figure 21 Utopia 1 Receive Handshake - RXCLAV Suspended Transfer (Byte Mode Only) Control and Status Interface

DPI Interface Option

The DPI interface is relatively new and worth additional description. The biggest difference between the DPI configurations and the UTOPIA config-

urations is that each channel has its own DPI interface. Each interface has a 4-bit data path, a clock and a start-of-cell signal, for both the transmit

direction and the receive direction. Therefore, each signal is point-to-point, and none of these signals has high-Z capability. Additionally, there is one

master DPI clock input (DPICLK) into the 77V1254L25 which is used as a source for the DPI transmit clock outputs. DPI is a cell-based transfer

scheme like Utopia Level 2, whereas UTOPIA Level 1 transfers can be either byte- or cell-based.

Another unique aspect of DPI is that it is a symmetrical interface. It is as easy to connect two PHYs back-to-back as it is to connect a PHY to a

switch fabric chip. In contrast, Utopia is asymmetrical. Note that for the 77V1254L25 the nomenclature "transmit" and "receive" is used in the naming

of the DPI signals, whereas other devices may use more generic "in" and "out" nomenclature for their DPI signals.

The DPI signals are summarized below, where "Pn_" refers to the signals for channel number "n":

DPICLK

input to PHY

Pn_TCLK

PHY to ATM

Pn_TD[3:0]

ATM to PHY

Pn_TFRM

ATM to PHY

Pn_RCLK

ATM to PHY

Pn_RD[3:0]

PHY to ATM

Pn_RFRM

PHY to ATM

(+

(

(!>@

RXEN

>@

(!!>$@B

('!()*

'"%

'""

'"

;56G7

;56G7

'"

'"

'"#

'"$

;56G7

;56G7

(E! =54 5 #B 065808 E B E B E B E

.

(+

(

(!>@

RXEN

>@

(!!>$@B

('!()*

;

;

;56G7

;56G7

;

;"

;

'

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT79RC64V475250DZ | RISControllerTM Embedded 64-bit Microprocessor, based on RISCore4000 |

| IDT79RC64V475250DZI | RISControllerTM Embedded 64-bit Microprocessor, based on RISCore4000 |

| IDT79RC64V474180DZI | RISControllerTM Embedded 64-bit Microprocessor, based on RISCore4000 |

| IDT79RC64V475180DZI | RISControllerTM Embedded 64-bit Microprocessor, based on RISCore4000 |

| IDT79RC64V474200DZI | RISControllerTM Embedded 64-bit Microprocessor, based on RISCore4000 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT77V252L155PG | 制造商:Integrated Device Technology Inc 功能描述:ATM/SONET SEGMENTATION AND REASSEMBLY CIRCUIT, 208 Pin, Plastic, QFP |

| IDT77V400S156BC | 功能描述:IC SW MEMORY 8X8 1.2BGPS 256-BGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:SwitchStar™ 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT77V400S156BCG | 功能描述:IC SW MEMORY 8X8 1.2BGPS 256-BGA RoHS:是 類別:集成電路 (IC) >> 專用 IC 系列:SwitchStar™ 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT77V400S156DS | 功能描述:IC SW MEMORY 8X8 1.2BGPS 208PQFP RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:SwitchStar™ 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT77V500S25BC | 功能描述:IC SW MEMORY 8X8 1.2BGPS 144-BGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:SwitchStar™ 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。