- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360859 > IMST425-J25S 32-Bit Microprocessor PDF資料下載

參數(shù)資料

| 型號(hào): | IMST425-J25S |

| 元件分類: | 32位微控制器 |

| 英文描述: | 32-Bit Microprocessor |

| 中文描述: | 32位微處理器 |

| 文件頁(yè)數(shù): | 33/74頁(yè) |

| 文件大?。?/td> | 563K |

| 代理商: | IMST425-J25S |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)當(dāng)前第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)

5 External memory interface

/ 74

33

MemnotWrD0

MemnotRfD1

MemAD2

MemAD3

MemAD31

MemConfig

MemConfig

64

periods

of

ClockIn

Periods of ClockIn

16

periods

of

ClockIn

Read at

7FFFFF6C

Read at

7FFFFF70

Delay

Internal configuration

External configuration

0 00 0 11

2 46 8 02

6 6 6

0 2 4

5

8

1

2

Internal configuration:

MemConfig

connected to

MemAD2

External configuration:

MemConfig

connected to inverse of

MemAD3

1

2

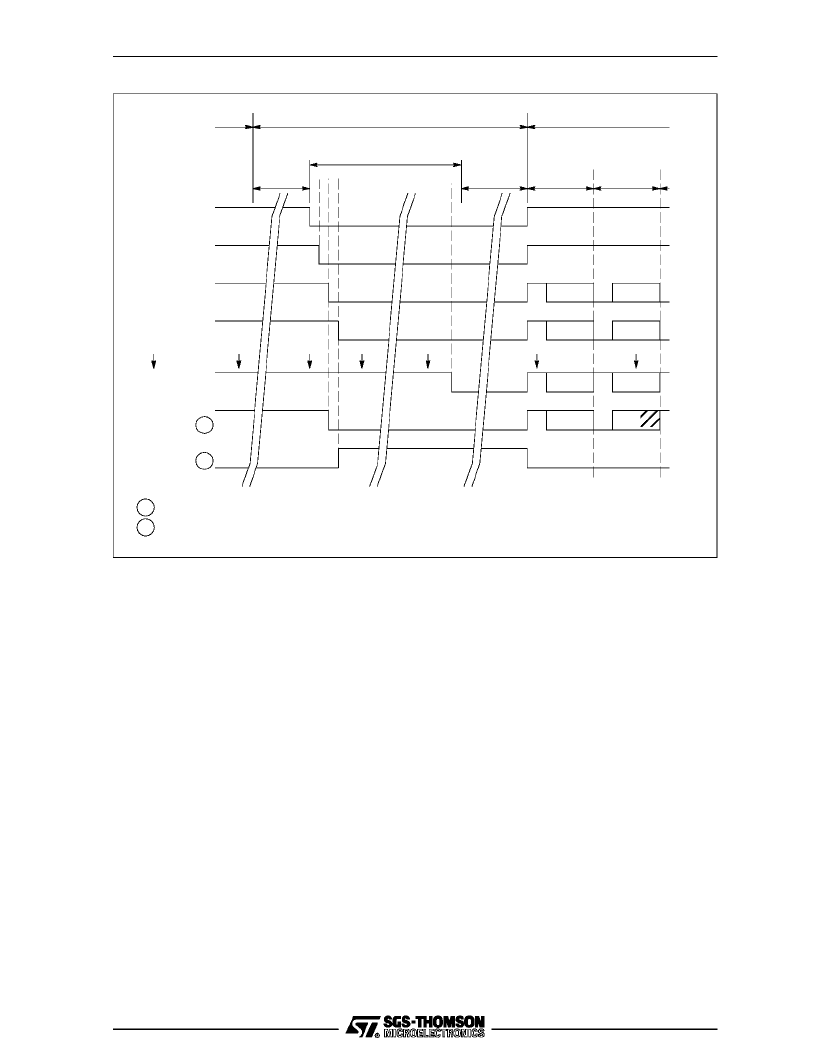

Figure 5.18

IMS T400 internal configuration scan

5.7.2

External configuration

If

MemConfig

isheldlowuntil

MemnotWrD0

goeslowtheinternalconfigurationisignoredand anexternal

configuration will be loaded instead. An external configuration scan always follows an internal one, but if

an internal configuration occurs any external configuration is ignored.

Theexternal configurationscancomprises36 successiveexternalreadcycles,using thedefaultEMI con-

figuration preset by

MemAD31

. However,instead ofdata beingreadon thedatabus asfor a normalread

cycle, onlya singlebit ofdatais readon

MemConfig

at eachcycle. Addressesputout onthebus foreach

read cycle are shown intable 5.10,and aredesigned to address ROM atthe topof the memory map. The

table shows the data to be held in ROM; data required at the

MemConfig

pin is the inverse of this.

MemConfig

is typically connected via an inverter to

MemnotWrD0

. Data bit zero of the least significant

byte of each ROM word then provides the configuration data stream. By switching

MemConfig

between

variousdatabuslines upto32 configurationscanbestoredinROM,one perbitof thedatabus.

MemCon-

fig

can be permanently connected to a data line or to

GND

. Connecting

MemConfig

to

GND

gives all

Tstates

configured to four periods;

notMemS1

pulse of maximum duration;

notMemS2-4

delayed by

maximum; refresh interval 72 periods of

ClockIn

; refresh enabled; late write.

The external memory configuration table 5.10 shows the contribution of each memory address to the

13 configurationfields. Thelowest12 words(#7FFFFF6C to#7FFFFF98, fields1 to 6)definethe number

of extra periods

Tm

to be added to each

Tstate

. If field 2 is 3 then three extra periods will be added to

T2

to extend it to the maximum of four periods.

The nextfive addresses (field 7) definetheduration of

notMemS1

and thefollowing fifteen (fields8 to 10)

definethe delaysbefore strobes

notMemS2-4

become active. Thefive bits allocatedto each strobeallow

durations of from 0 to 31 periods

Tm

, as described in strobes page 15.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IMST425-X25S | 32-Bit Microprocessor |

| IMST800C-G17S | Peripheral IC |

| IMST800C-G20S | Peripheral IC |

| IMST800C-G30S | Peripheral IC |

| IMST805-F20E | 32-Bit Microprocessor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IMST425-X25S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| IMST800C-G17S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| IMST800C-G20S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| IMST800C-G30S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| IMST801 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:IMST801 TRANSPUETR |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。