- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360859 > IMST425J20S Peripheral IC PDF資料下載

參數(shù)資料

| 型號: | IMST425J20S |

| 英文描述: | Peripheral IC |

| 中文描述: | 外圍芯片 |

| 文件頁數(shù): | 11/74頁 |

| 文件大?。?/td> | 563K |

| 代理商: | IMST425J20S |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁

3 System services

/ 74

11

3.9

Error, ErrorIn

The

Error

pin carries the OR’ed output of the internal Error flag and the

ErrorIn

input. If

Error

is high it

indicateseither that

ErrorIn

is high orthat anerrorwas detectedin oneof theprocesses. Aninternal error

canbe caused, for example,byarithmetic overflow,divide by zero,array bounds violationorsoftwareset-

ting the flag directly.Once set, theErrorflag isonly cleared by executingthe instruction testerr The error

is not cleared by processor reset, in order that analysis can identify any errant transputer (page 9).

Aprocesscan beprogrammedto stopif theErrorflagisset;itcannotthentransmiterroneousdatato other

processes, but processes which do not require that data can still be scheduled. Eventually all processes

which rely, directly or indirectly, on data from the process in error will stop through lack of data.

ErrorIn

does not directly affect the status of a processor in any way.

BysettingtheHaltOnErrorflagthetransputer itselfcanbeprogrammedtohaltifErrorbecomesset.IfError

becomessetafterHaltOnErrorhasbeenset, allprocesseson that transputerwillcease butwillnot neces-

sarily causeother transputersina network tohalt. SettingHaltOnErrorafterErrorwillnot causethe trans-

puterto halt;thisallowstheprocessorresetandanalysefacilitiestofunctionwith theflagsinindeterminate

states.

An alternative method of error handling is to have the errant process or transputer cause all transputers

to halt. This can be done by ‘daisy-chaining’ the

ErrorIn

and

Error

pins of a number of processors and

applying the final

Error

output signal to the

EventReq

pin of a suitably programmed master transputer.

Since the process state is preserved when stopped by an error, the master transputer can then use the

analysefunctionto debugthefault.Whenusingsuchacircuit,notethattheErrorflagisinanindeterminate

state on power up; the circuit and software should be designed with this in mind.

Error checks can be removed completely to optimise the performance of a proven program; any unex-

pected error then occurring will have an arbitrary undefined effect.

If a high priority process pre-empts a low priority one, status of the Errorand HaltOnErrorflags is saved

for thedurationof thehighpriority processandrestored atthe conclusionofit.Statusof bothflagsistrans-

mitted tothe highpriority process. Eitherflagcan be alteredinthe process withoutupsetting theerror sta-

tus of any complex operation being carried out by the pre-empted low priority process.

IntheeventofatransputerhaltingbecauseofHaltOnErrorthelinkswillfinishoutstandingtransfersbefore

shutting down. If

Analyse

is asserted then all inputs continue but outputs will not make another access

to memory for data. Memory refresh will continue to take place.

Afterhalting due totheErrorflag changingfrom 0 to 1 whilstHaltOnErroris set, register

I

pointstwo bytes

pastthe instructionwhichset Error Afterhaltingdue tothe

Analyse

pin being takenhigh, register

I

points

one byte past the instruction being executed. In both cases

I

will be copied to register

A

.

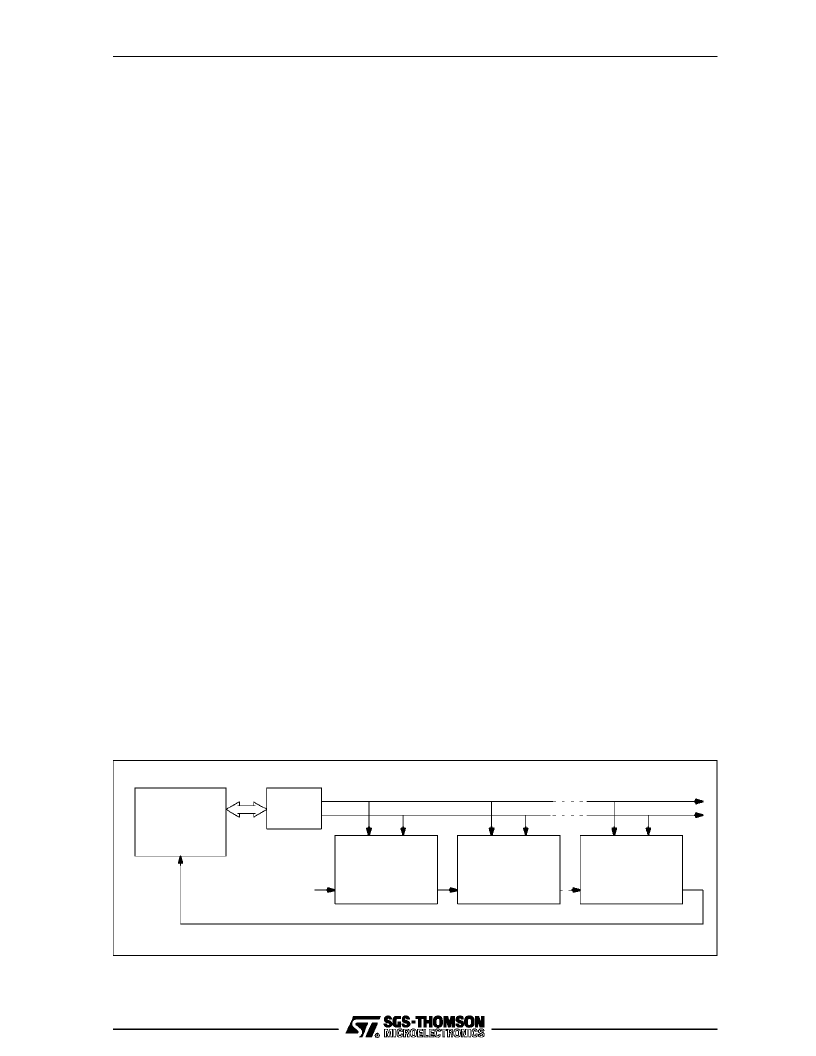

T805

slave 0

ErrorIn

Error

T400

slave 1

ErrorIn

Error

T805

slave n

ErrorIn

Error

Latch

Master

Transputer

EventReq

GND

(transputer links not shown)

Reset

Analyse

Figure 3.6

Error handling in a multi-transputer system

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IMST425-J20S | 32-Bit Microprocessor |

| IMST425-J25S | 32-Bit Microprocessor |

| IMST425-X25S | 32-Bit Microprocessor |

| IMST800C-G17S | Peripheral IC |

| IMST800C-G20S | Peripheral IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IMST425-J20S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| IMST425-J25S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| IMST425-X25S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| IMST800C-G17S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| IMST800C-G20S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。