- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360859 > IMST425J20S Peripheral IC PDF資料下載

參數(shù)資料

| 型號: | IMST425J20S |

| 英文描述: | Peripheral IC |

| 中文描述: | 外圍芯片 |

| 文件頁數(shù): | 18/74頁 |

| 文件大小: | 563K |

| 代理商: | IMST425J20S |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當(dāng)前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁

IMS T400

/ 74

18

5.2

Read cycle

Byteaddressingiscarriedout internallybythetransputer for readcycles. Forareadcycle thereadstrobe

notMemRd

is low during

T4

and

T5

. Read cycle data may be set up on the data bus at any timeafter the

start of

T3

, butmust be validwhen the transputerreadsit at theend of

T5

.Data mayberemoved any time

during

T6

, but must be off the bus no later than the end of that period.

notMemS0

isa fixedformatstrobe.Its leadingedgeisalwayscoincidentwith thestart of

T2

and its trailing

edge always coincident with the end of

T5

.

Theleadingedgeof

notMemS1

isalwayscoincidentwiththestartof

T2

, butitsdurationmaybeconfigured

to be fromzero to 31 periods

Tm

. Regardlessofthe configuredduration, the strobe willterminate no later

than theendof

T6

. Thestrobe issometimes programmed toextendbeyond thenormalend of

Tmx

. When

wait states are inserted into an EMI cycle the end of

Tmx

is delayed, but the potential active duration of

the strobeis notaltered.Thus thestrobe canbe configuredto terminaterelatively early undercertain con-

ditions (page 24). If

notMemS1

is configured to be zero it will never go low.

notMemS2

,

notMemS3

and

notMemS4

are identical in operation. They all terminate at the end of

T5

,

but the start of each can be delayed from one to 31 periods

Tm

beyond the start of

T2

. If the duration of

one of these strobes would take it past the end of

T5

it will stay high. This canbe used to cause a strobe

to become active only when wait states are inserted. If one of these strobes is configured to zero it will

remain low during

T1

–

T5

and only go high during the first

Tm

of

T6

. Figure 5.6 shows the effect of

Wait

on strobes in more detail; each division on the scale is one period

Tm

.

In theread cycle timing diagrams

ProcClockOut

is included as aguide only;it isshown witheach

Tstate

configured to one period

Tm

.

T400-20

Min

0

25

0

a

–4

–4

b

–3

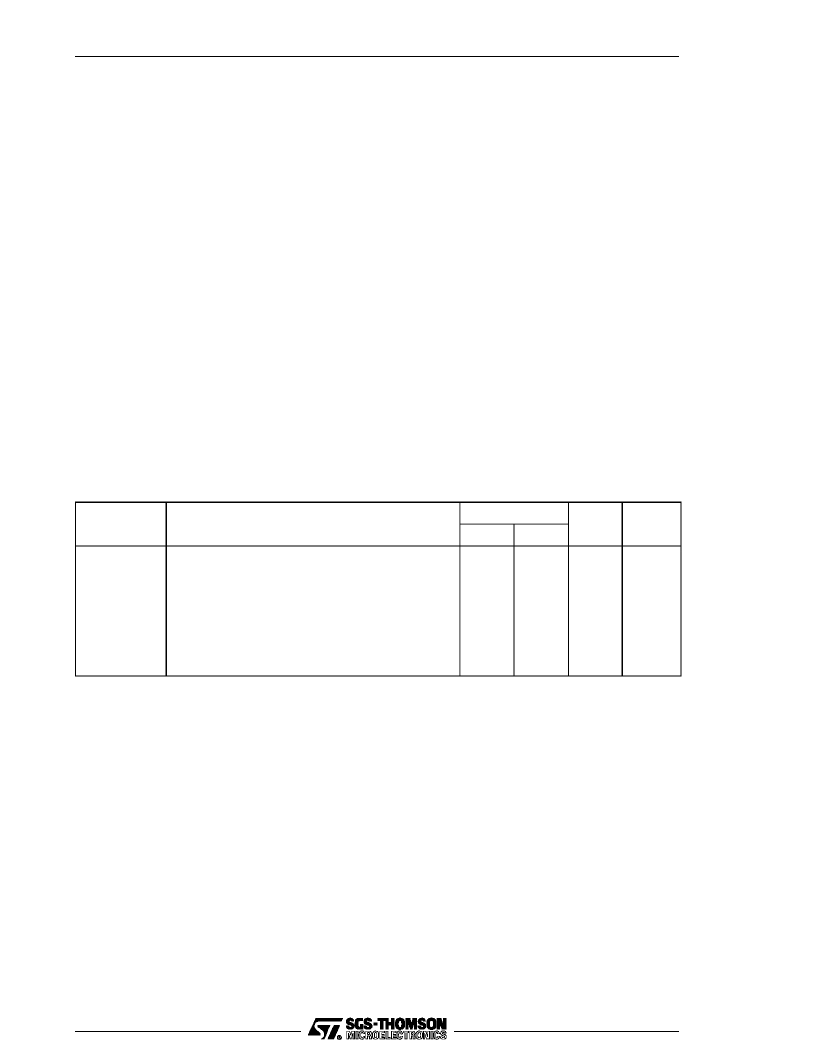

Symbol

TaZdV

TdVRdH

TRdHdX

TS0LRdL

TS0HRdH

TRdLRdH

Parameter

Address tristate to data valid

Data setup before read

Data hold after read

notMemS0

before start of read

End of read from end of

notMemS0

Read period

Max

Units

ns

ns

ns

ns

ns

ns

Notes

a

+4

4

b

+5

1

2

Notes

1

a

is total of

T2

+

T3

where

T2

,

T3

can be from one to four periods

Tm

each in length.

2

b

is total of

T4

+

Twait

+

T5

where

T4

,

T5

can be from one to four periods

Tm

each in length and

Twait

may be any number of periods

Tm

in length.

Table5.2

Read

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IMST425-J20S | 32-Bit Microprocessor |

| IMST425-J25S | 32-Bit Microprocessor |

| IMST425-X25S | 32-Bit Microprocessor |

| IMST800C-G17S | Peripheral IC |

| IMST800C-G20S | Peripheral IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IMST425-J20S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| IMST425-J25S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| IMST425-X25S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| IMST800C-G17S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| IMST800C-G20S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。