- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377496 > Intel387 sx (Intel Corp.) SX Math Coprocessor(32位數(shù)學(xué)協(xié)處理器) PDF資料下載

參數(shù)資料

| 型號(hào): | Intel387 sx |

| 廠商: | Intel Corp. |

| 英文描述: | SX Math Coprocessor(32位數(shù)學(xué)協(xié)處理器) |

| 中文描述: | 山西數(shù)學(xué)協(xié)處理器(32位數(shù)學(xué)協(xié)處理器) |

| 文件頁數(shù): | 12/47頁 |

| 文件大小: | 443K |

| 代理商: | INTEL387 SX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當(dāng)前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁

Intel387

TM

SX MATH COPROCESSOR

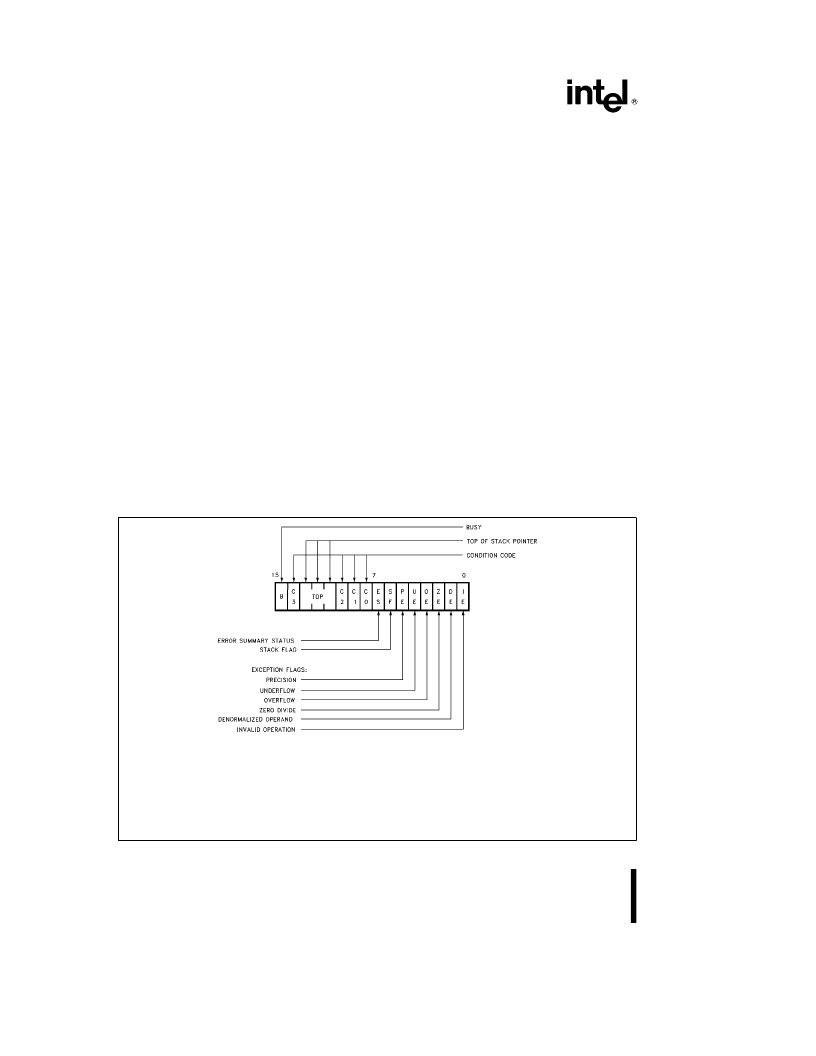

3.2.1 STATUS WORD (SW) REGISTER

The 16-bit status word (in the status register) shown

in Figure 3-2 reflects the overall state of the Math

CoProcessor. It can be read and inspected by pro-

grams using the FSTSW memory or FSTSW AX in-

structions.

Bit 15, the Busy bit (B) is included for 8087 compati-

bility only. It always has the same value as the Error

Summary bit (ES, bit 7 of status word); it does not

indicate the status of the BUSY

Y

output of the Math

CoProcessor.

Bits 13–11 (TOP) serves as the pointer to the Math

CoProcessor data register that is the current Top-Of-

Stack. The significance of the stack top is described

in Section 3.2.5 Data Registers.

The four numeric condition code bits (C

3

–C

0

, Bit 14,

10–8) are similar to the flags in a CPU; instructions

that perform arithmetic operations update these bits

to reflect the outcome. The effects of the instruc-

tions on the condition code are summarized in Ta-

bles 3-1 through 3-4. These condition code bits are

used principally for conditional branching. The

FSTSW AX instructions stores the Math CoProces-

sor status word directly to the CPU AX register, al-

lowing the condition codes to be inspected efficient-

ly by Intel386 CPU code. The Intel386 CPU SAHF

instruction can copy C

3

–C

0

directly to the flag bits to

simplify conditional branching. Table 3-5 shows the

mapping of these bits to the Intel386 CPU flag bits.

Bit 7 is the error summary (ES) status bit. This bit is

set if any unmasked exception bit is set; it is clear

otherwise. If this bit is set, the ERROR

Y

signal is

asserted.

Bit 6 is the stack flag (SF). This bit is used to distin-

guish invalid operations due to stack overflow or un-

derflow from other kinds of invalid operations. When

SF is set, bit 9 (C

1

) distinguishes between stack

overflow (C

1

e

1) or underflow (C

1

e

0).

Bit 5–0 are the six exception flags of the status word

and are set to indicate that during an instruction exe-

cution the Math CoProcessor has detected one of

six possible exception conditions since these status

bits were last cleared or reset. Section 3.5 entitled

Exception Handling explains how they are set and

used.

The exception flags are ‘‘sticky’’ bits and can only

be cleared by the instructions FINIT, FCLEX,

FLDENV, FSAVE, and FRSTOR. Note that when a

new value is loaded into the status word by the

FLDENV or FRSTOR instruction, the value of ES (bit

7) and B (bit 15) are not derived from the values

loaded from memory but rather are dependent upon

the values of the exception flags (bits 5–0) in the

status word and their corresponding masks in the

control word. If ES is set in such a case, the

ERROR

Y

output of the Math CoProcessor is acti-

vated immediately.

240225–3

ES is set if any unmasked exception bit is set; cleared otherwise. See Table 2-2 for interpretation of condition code.

TOP values:

000

e

Register 0 is Top of Stack

001

e

Register 1 is Top of Stack

.

.

.

111

e

Register 7 is Top of Stack

For definitions of exceptions, refer to the section entitled ‘‘Exception Handling’’

Figure 3-2. Status Word

12

12

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| INTEL486 GX | Emedded Ultra-Low Power INTEL486 GX Processor(嵌入式超低能量處理器) |

| INTEL486 SX | Emedded Ultra-Low Power INTEL486 SX Processor(嵌入式超低能量處理器) |

| INTEL82801 | 82801AB (ICH0) I/O Controller Hub |

| INTEL82802AB | Firmware Hub (FWH) |

| INTELDX2 | High-Performance 32-Bit Embedded Processor(高性能32位嵌入式處理器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| INTEL387TMDX | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel387TM DX MATH COPROCESSOR |

| INTEL740 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Graphics (GUI) Accelerator |

| INTEL82801 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:82801AB (ICH0) I/O Controller Hub |

| INTEL82802AB | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Firmware Hub (FWH) |

| INTELLIGENT CHARGER + 4AA | 制造商:Energizer 功能描述:Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。