- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383129 > ISL3873AIK-TK (INTERSIL CORP) JT 32C 32#20 PIN WALL RECP PDF資料下載

參數(shù)資料

| 型號(hào): | ISL3873AIK-TK |

| 廠商: | INTERSIL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | JT 32C 32#20 PIN WALL RECP |

| 中文描述: | 1 CHANNEL(S), 11M bps, LOCAL AREA NETWORK CONTROLLER, PBGA192 |

| 封裝: | 14 X 14 MM, PLASTIC, BGA-192 |

| 文件頁(yè)數(shù): | 33/42頁(yè) |

| 文件大小: | 778K |

| 代理商: | ISL3873AIK-TK |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)當(dāng)前第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)

33

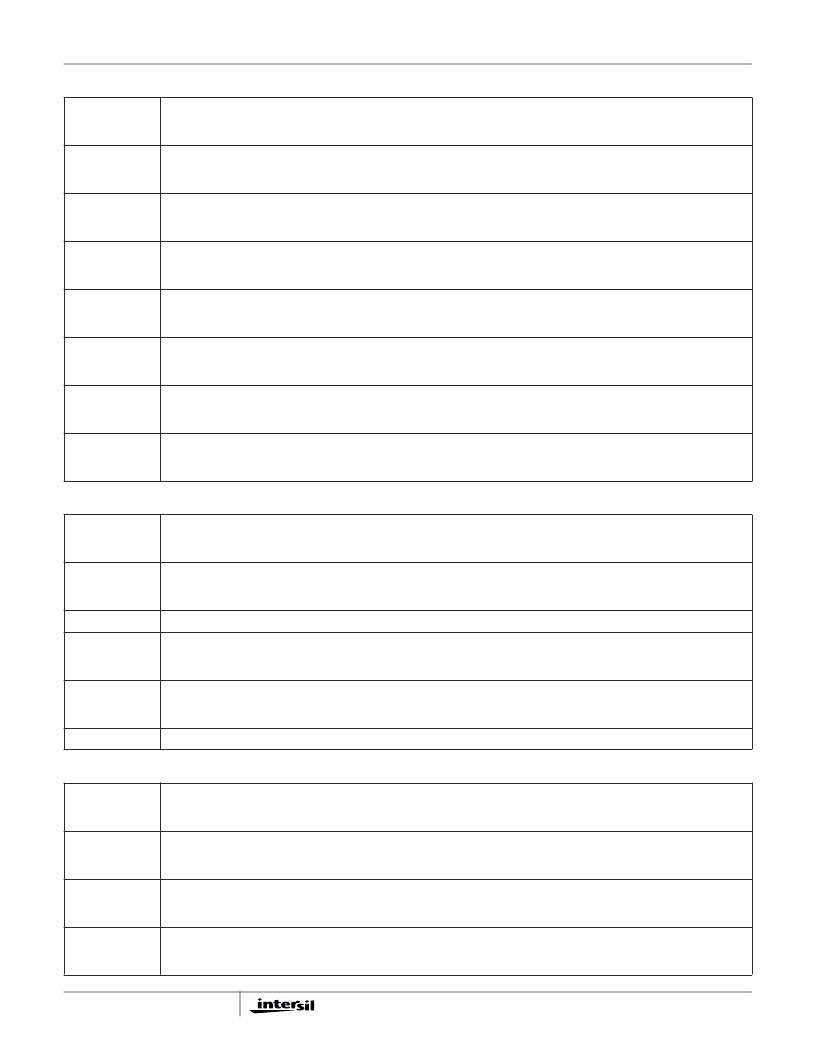

CONFIGURATION REGISTER 10 ADDRESS (14h) R/W RX CONFIGURE

Bit 7

AGC freeze during packet.

0 = Disable (do not disable unless MAC can handle baseband processor aborting during MPDU reception).

1 = Enable.

Bit 6

CIR estimate/ Dot product clock control.

0 = on during acquisition.

1 = only on after detect.

Bit 5

ISI equalizer control.

0 = enable equalizer.

1 = disable equalizer.

Bit 4

ICI equalizer control.

0 = enable equalizer.

1 = disable equalizer.

Bit 3

MD_RDY control.

0 = After CRC16.

1 = After SFD.

Bit 2

Slot diversity mode control.

0 = disabled, Antenna diversity on for entire slot.

1 = enabled, Antenna diversitydisabled for last half of slot - saves acquisition time, use in system where nodes are slot aligned.

Bit 1

Antenna choice for Receiver when single antenna acquisition is selected.

0 = Antenna select pin low.

1 = Antenna select pin high.

Bit 0

Single or dual antenna acquire.

0 = dual antenna for diversity acquisition.

1 = single antenna.

CONFIGURATION REGISTER 11 ADDRESS (16h) R/W RX-TX CONFIGURE

Bit 7

Continuous internal RX 22 and 44MHz clocks; (Only Reset active will stop).

0 = normal.

1 = continuous, overrides CR10 bit 6.

Bit 6

A/D input coupling.

0 = DC.

1 = AC (external bias network required).

Bit 5

Reserved.

Bit 4

Short Preamble test mode.

0 = use CR3 for short preamble.

1 = run TX and RX short preamble using preamble length in CR4.

Bit 3

CCA mode.

0 = normal (raw) mode CCA. CCA will immediately respond to changes in ED, CS1, and SQ1 as configured.

1 = Sampled mode CCA. CCA will update once per slot (20

μ

s), will be valid at 18.7

μ

s or 15.8

μ

s as determined by CR9 bit 7.

Bits 2:0

Precursor value in CIR estimate.

CONFIGURATION REGISTER 12 ADDRESS (18h) R/W A/D TEST MODES 1

Bit 7

All DAC and A/D clock source control.

0 = normal internal clocks.

1 = clock via SDI pin.

Bit 6

TX DAC clock.

0 = enable.

1 = disable.

Bit 5

RX DAC clock.

0 = enable.

1 = disable.

Bit 4

I DAC clock.

0 = enable.

1 = disable.

ISL3873A

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISL3873A | Wireless LAN Integrated Medium Access Controller with Baseband Processor |

| ISL3873AIK | RES 0805 1/8W 5% 1.2KOHM |

| ISL3874IK96 | Wireless LAN Integrated Medium Access Controller with Baseband Processor with Mini-PCI |

| ISL3874 | Wireless LAN Integrated Medium Access Controller with Baseband Processor with Mini-PCI |

| ISL3874IK | Wireless LAN Integrated Medium Access Controller with Baseband Processor with Mini-PCI |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISL3873BIK | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Intersil Corporation 功能描述: |

| ISL3873BIK-TK | 制造商:Intersil Corporation 功能描述:1 CHANNEL(S), 11M bps, LOCAL AREA NETWORK CONTROLLER, PBGA192 |

| ISL3873IK | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Wireless LAN Integrated Medium Access Controller with Baseband Processor |

| ISL3873IK96 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Wireless LAN Integrated Medium Access Controller with Baseband Processor |

| ISL3874 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Wireless LAN Integrated Medium Access Controller with Baseband Processor with Mini-PCI |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。