- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄10588 > ISLA222P20IRZ (Intersil)IC ADC 12BIT SRL/SPI 72QFN PDF資料下載

參數(shù)資料

| 型號(hào): | ISLA222P20IRZ |

| 廠商: | Intersil |

| 文件頁數(shù): | 17/33頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC ADC 12BIT SRL/SPI 72QFN |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | FemtoCharge™ |

| 位數(shù): | 12 |

| 采樣率(每秒): | 200M |

| 數(shù)據(jù)接口: | 串行,SPI? |

| 轉(zhuǎn)換器數(shù)目: | 2 |

| 功率耗散(最大): | 830mW |

| 電壓電源: | 模擬和數(shù)字 |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 72-VFQFN 裸露焊盤 |

| 供應(yīng)商設(shè)備封裝: | 72-QFN(10x10) |

| 包裝: | 托盤 |

| 輸入數(shù)目和類型: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁

ISLA222P

24

FN7853.1

June 17, 2011

and N-byte transfers, respectively. The operation for a 3-byte

transfer can be inferred from these diagrams.

SPI Configuration

ADDRESS 0X00: CHIP_PORT_CONFIG

Bit ordering and SPI reset are controlled by this register. Bit order

can be selected as MSB to LSB (MSB first) or LSB to MSB (LSB

first) to accommodate various micro controllers.

Bit 7 SDO Active

Bit 6 LSB First

Setting this bit high configures the SPI to interpret serial data

as arriving in LSB to MSB order.

Bit 5 Soft Reset

Setting this bit high resets all SPI registers to default values.

Bit 4 Reserved

This bit should always be set high.

Bits 3:0 These bits should always mirror bits 4:7 to avoid

ambiguity in bit ordering.

ADDRESS 0X02: BURST_END

If a series of sequential registers are to be set, burst mode can

improve throughput by eliminating redundant addressing. In

3-wire SPI mode, the burst is ended by pulling the CSB pin high. If

the device is operated in 2-wire mode the CSB pin is not

available. In that case, setting the burst_end address determines

the end of the transfer. During a write operation, the user must

be cautious to transmit the correct number of bytes based on the

starting and ending addresses.

Bits 7:0 Burst End Address

This register value determines the ending address of the burst

data.

Device Information

ADDRESS 0X08: CHIP_ID

ADDRESS 0X09: CHIP_VERSION

The generic die identifier and a revision number, respectively, can

be read from these two registers.

Device Configuration/Control

A common SPI map, which can accommodate single-channel or

multi-channel devices, is used for all Intersil A/D products.

ADDRESS 0X20: OFFSET_COARSE_ADC0

ADDRESS 0X21: OFFSET_FINE_ADC0

The input offset of the A/D core can be adjusted in fine and

coarse steps. Both adjustments are made via an 8-bit word as

detailed in Table 5. The data format is twos complement.

The default value of each register will be the result of the

self-calibration after initial power-up. If a register is to be

incremented or decremented, the user should first read the

register value then write the incremented or decremented value

back to the same register.

ADDRESS 0X22: GAIN_COARSE_ADC0

ADDRESS 0X23: GAIN_MEDIUM_ADC0

ADDRESS 0X24: GAIN_FINE_ADC0

Gain of the A/D core can be adjusted in coarse, medium and fine

steps. Coarse gain is a 4-bit adjustment while medium and fine

are 8-bit. Multiple Coarse Gain Bits can be set for a total

adjustment range of ±4.2%. (‘0011’

-4.2% and ‘1100’ +4.2%)

It is recommended to use one of the coarse gain settings (-4.2%,

-2.8%, -1.4%, 0, 1.4%, 2.8%, 4.2%) and fine-tune the gain using the

registers at 0x0023 and 0x24.

The default value of each register will be the result of the

self-calibration after initial power-up. If a register is to be

incremented or decremented, the user should first read the

register value then write the incremented or decremented value

back to the same register.

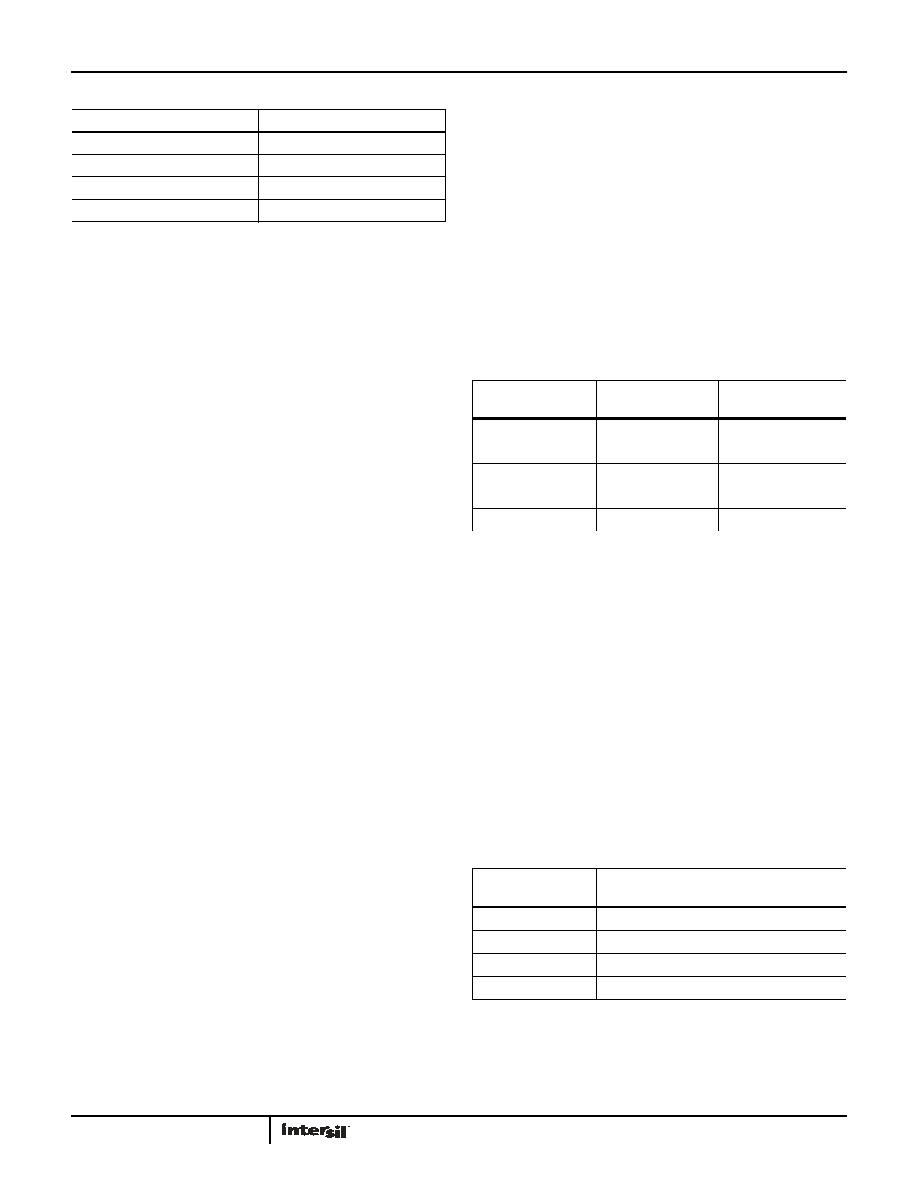

TABLE 4. BYTE TRANSFER SELECTION

[W1:W0]

BYTES TRANSFERRED

00

1

01

2

10

3

11

4 or more

TABLE 5. OFFSET ADJUSTMENTS

PARAMETER

0x20[7:0]

COARSE OFFSET

0x21[7:0]

FINE OFFSET

Steps

255

–Full-Scale (0x00)

-133LSB (-47mV)

-5LSB (-1.75mV)

Mid–Scale (0x80)

0.0LSB (0.0mV)

0.0LSB

+Full-Scale (0xFF)

+133LSB (+47mV)

+5LSB (+1.75mV)

Nominal Step Size

1.04LSB (0.37mV)

0.04LSB (0.014mV)

TABLE 6. COARSE GAIN ADJUSTMENT

0x22[3:0] CORE 0

0x26[3:0] CORE 1

NOMINAL COARSE GAIN ADJUST

(%)

Bit3

+2.8

Bit2

+1.4

Bit1

-2.8

Bit0

-1.4

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LMH0002TMAX/NOPB | IC CABLE DVR SERIAL DGTL 8-SOIC |

| KAD2710L-27Q68 | IC ADC 10BIT 275MSPS SGL 68-QFN |

| VE-27L-IW-F4 | CONVERTER MOD DC/DC 28V 100W |

| LMH0002SQX/NOPB | IC CABLE DVR SERIAL DGTL 16-LLP |

| LMH0002MAX/NOPB | IC CABLE DRIVER DGTL 8-SOIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISLA222P25 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Dual 14-Bit, 250MSPS/200MSPS/130MSPS ADC |

| ISLA222P25IRZ | 制造商:Intersil Corporation 功能描述:12-BIT 250MSPS DUAL ADC, 72-PIN QFN - Trays 制造商:Intersil Corporation 功能描述:IC ADC 12BIT SRL/SPI 72QFN 制造商:Intersil 功能描述:12-BIT 250MSPS DL AD C 72-PIN |

| ISLA222S | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Dual 12-Bit, 250/200/125 MSPS JESD204B High Speed Serial Output ADC |

| ISLA222S12 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Dual 14-Bit, 250/200/125 MSPS JESD204B High Speed Serial Output ADC |

| ISLA222S12IR1Z | 制造商:Intersil Corporation 功能描述:DUAL 12-BIT, 125MSPS ADC W/HIGH SPEED SERIAL JESD204B OUTPUT - Trays 制造商:Intersil Corporation 功能描述:IC ADC 12BIT SPI/SRL 125M 48LQFN |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。