- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373088 > K9F1G08R0A (SAMSUNG SEMICONDUCTOR CO. LTD.) Circular Connector; MIL SPEC:MIL-DTL-38999 Series III; Body Material:Metal; Series:TVP00; No. of Contacts:99; Connector Shell Size:25; Connecting Termination:Crimp; Circular Shell Style:Wall Mount Receptacle; Body Style:Straight PDF資料下載

參數(shù)資料

| 型號(hào): | K9F1G08R0A |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 元件分類: | 圓形連接器 |

| 英文描述: | Circular Connector; MIL SPEC:MIL-DTL-38999 Series III; Body Material:Metal; Series:TVP00; No. of Contacts:99; Connector Shell Size:25; Connecting Termination:Crimp; Circular Shell Style:Wall Mount Receptacle; Body Style:Straight |

| 中文描述: | 128M的× 8位/ 256M × 8位NAND閃存 |

| 文件頁(yè)數(shù): | 31/37頁(yè) |

| 文件大?。?/td> | 1008K |

| 代理商: | K9F1G08R0A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)當(dāng)前第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)

31

K9F1G08U0A

K9F1G08R0A

K9K2G08U1A

FLASH MEMORY

Cache Program

Cache Program is an extension of Page Program, which is executed with 2112byte data registers, and is available only within a block.

Since the device has 1 page of cache memory, serial data input may be executed while data stored in data register are programmed

into memory cell.

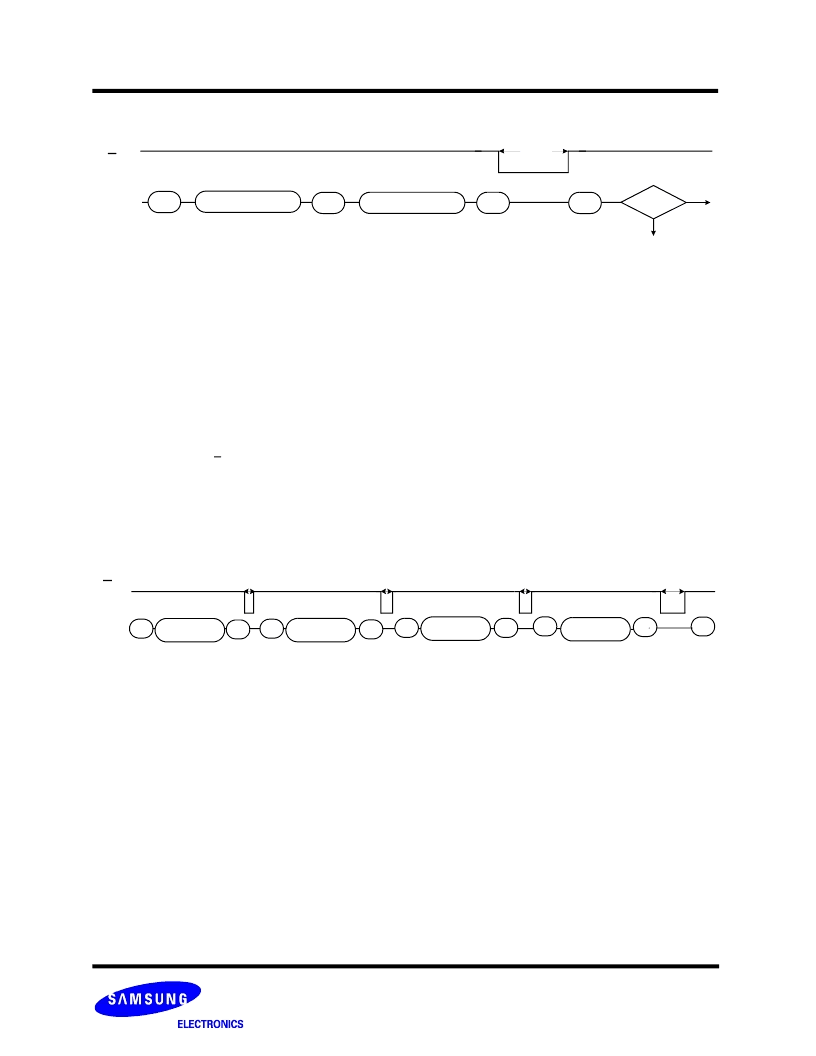

Figure 9. Random Data Input In a Page

80h

R/B

Address & Data Input

I/O

0

Pass

10h

70h

Fail

t

PROG

85h

Address & Data Input

After writing the first set of data up to 2112byte into the selected cache registers, Cache Program command (15h) instead of actual

Page Program (10h) is inputted to make cache registers free and to start internal program operation. To transfer data from cache reg-

isters to data registers, the device remains in Busy state for a short period of time(tCBSY) and has its cache registers ready for the

next data-input while the internal programming gets started with the data loaded into data registers. Read Status command (70h) may

be issued to find out when cache registers become ready by polling the Cache-Busy status bit(I/O 6). Pass/fail status of only the pre-

viouse page is available upon the return to Ready state. When the next set of data is inputted with the Cache Program command,

tCBSY is affected by the progress of pending internal programming. The programming of the cache registers is initiated only when the

pending program cycle is finished and the data registers are available for the transfer of data from cache registers. The status bit(I/

O5) for internal Ready/Busy may be polled to identify the completion of internal programming. If the system monitors the progress of

programming only with R/B, the last page of the target programming sequence must be progammed with actual Page Program com-

mand (10h).

Figure 10. Cache Program

(available only within a block)

t

CBSY

80h

R/B

80h

Address &

Data Input

15h

80h

Address &

Data Input

15h

80h

Address &

Data Input

10h

t

CBSY

t

CBSY

t

PROG

70h

Address &

Data Input*

15h

I/Ox

Col Add1,2 & Row Add1,2

Data

Col Add1,2

Data

Col Add1,2 & Row Add1,2

Data

Col Add1,2 & Row Add1,2

Data

Col Add1,2 & Row Add1,2

Data

Col Add1,2 & Row Add1,2

Data

"0"

"1"

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K9K2G16Q0M-YIB0 | 256M x 8 Bit / 128M x 16 Bit NAND Flash Memory |

| K9K2G16U0M-PCB0 | 256M x 8 Bit / 128M x 16 Bit NAND Flash Memory |

| K9K2G16U0M-PIB0 | 256M x 8 Bit / 128M x 16 Bit NAND Flash Memory |

| K9K2G16U0M-YCB0 | 256M x 8 Bit / 128M x 16 Bit NAND Flash Memory |

| K9K2G16U0M-YIB0 | 256M x 8 Bit / 128M x 16 Bit NAND Flash Memory |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K9F1G08R0B-JIB0000 | 制造商:Samsung SDI 功能描述:PN may be NE SE |

| K9F1G08U0A | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128M x 8 Bit / 256M x 8 Bit NAND Flash Memory |

| K9F1G08U0B-PCB0000 | 制造商:Samsung SDI 功能描述: 制造商:Samsung Semiconductor 功能描述:1GB SLC NORMAL X8 TSOP1 - Trays |

| K9F1G08U0B-PCB0T00 | 制造商:Samsung Semiconductor 功能描述:FLASH PARALLEL 3.3V 1GBIT 128MX8 48TSOP-I - Tape and Reel |

| K9F1G08U0B-PCBO | 制造商:Samsung 功能描述:Memory,NAND,1G,128MX8,48TSOP |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。