- 您現(xiàn)在的位置:買賣IC網 > PDF目錄69003 > L6260 (STMICROELECTRONICS) DISK DRIVE MOTOR CONTROLLER, 1.5 A, PQFP64 PDF資料下載

參數資料

| 型號: | L6260 |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | 運動控制電子 |

| 英文描述: | DISK DRIVE MOTOR CONTROLLER, 1.5 A, PQFP64 |

| 封裝: | TQFP-64 |

| 文件頁數: | 9/30頁 |

| 文件大小: | 440K |

| 代理商: | L6260 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁

The duration of the brake delay is defined by an

external resistor and capacitor connected to the

brake delay pin (BRK_DLY). Charge stored in an

external capacitor connected to the Voltage Tri-

pler (VPDOWN) is used to supply the brake delay

circuit after the loss of power.

During the application of power to the IC, the

power on reset signal (POR) is asserted, forcing

all registers to their default state (see @POR col-

umn of the register definitions) and disabling the

VCM and spindle drivers. Once the supply volt-

age has exceeded the Voltage Good (VGT)

threshold, the POR delay begins. When this delay

has expired, POR is de-asserted. It is this delay

whose duration is determined by an external ca-

pacitor connected to the POR_DLY pin.

When a low voltage condition is detected (the

supply voltage falls below the VGT) the following

happens (in order):

1)

Internal registers are reset and POR is as-

serted.

2) The automatic parking of the actuator is en-

abled and the brake delay starts.

3) After the brake delay expires, all low side driv-

ers are enabled to brake the spindle.

Serial Interface

The serial interface is designed to be compatible

with the Intel 80196 (and other similar micros) se-

rial interface but is capable of faster data rates,

up to 10 MHz. All read and write operations must

consist of 16 bits, with the 80196 this would be

two 8 bit accesses. The first four bits are address

and the next 12 are data. If the address is a read

register then the L6260 will use the SCLK from

the system to shift out 12 bits of data from the ad-

dressed register. The system must provide 16

SCLK pulses to insure that the read operation

completes.

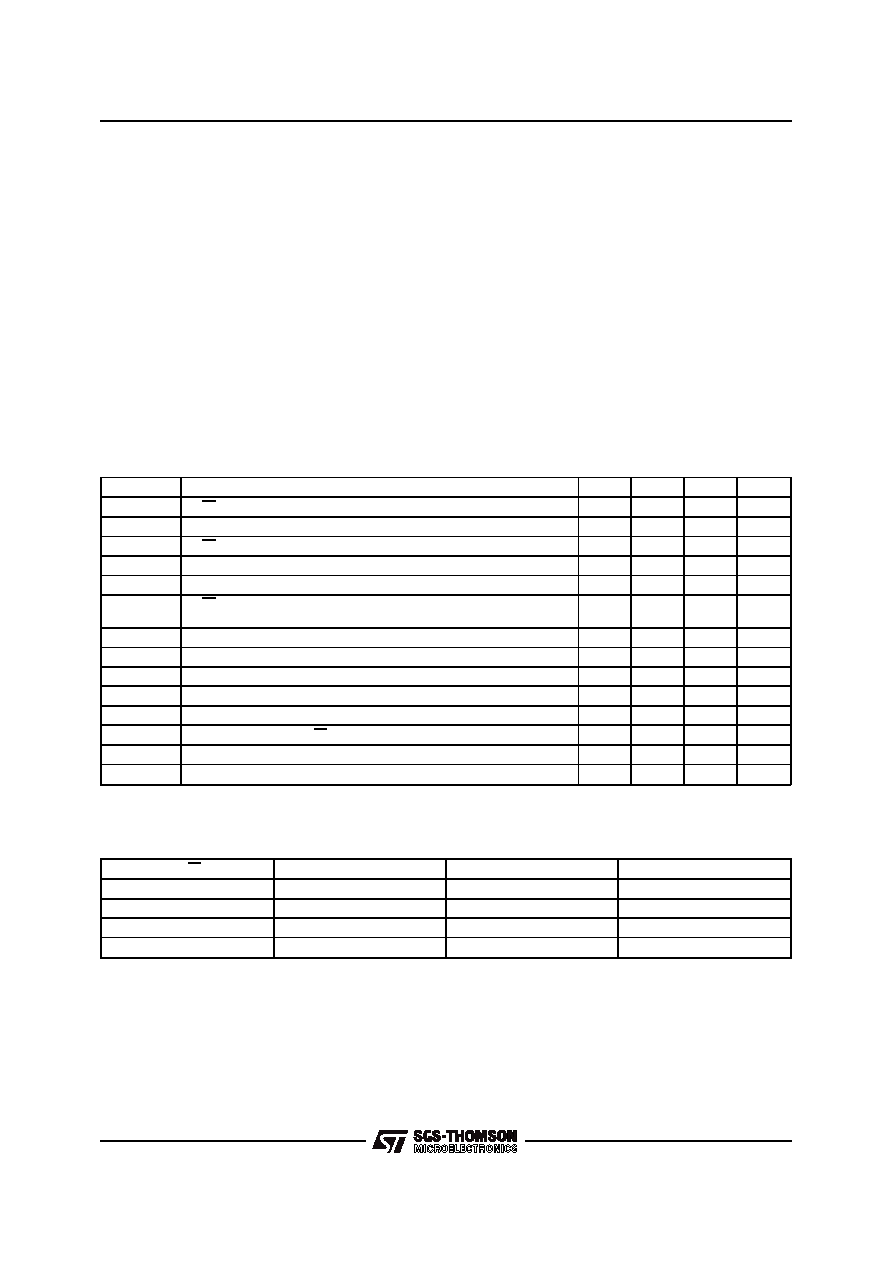

SYMBOL

DESCRIPTION

MIN.

TYP.

MAX.

UNITS

tRWS

R/W setup time to SCLK going high

100

ns

tSLS

SLOAD setup time to SCLK going high

100

ns

tRWH

R/W hold time after SCLK going high

100

ns

tSLH

SLOAD hold time after SCLK going high

100

ns

tSCKD

SCLK high to Data Valid

30

50

ns

tRWD

R/W High to Data Valid

Data bit D[0] valid from HiZ

30

50

ns

tAS

Address setup time to SCLK going high

30

ns

tDS

Data setup time to SCLK going High

30

ns

tAH

Address Hold after SCLK going high

10

ns

tDH

Data Hold time after SCLK going High

10

ns

tSDZ

SDIO tri-state after SLOAD going High

30

ns

tRWZ

SDIO tri-state after R/W going low

30

ns

tPER

Minimum SCLK period

100

ns

tREC (*)

Recycle - Time between successive accesses

100

ns

(*) For 10MHz system clock operation (in other words. 1 or more clock cycles of SCLK).

Serial Interface Truth Table

R/W

SLOAD

SDIO

DIRECTION

1

Tri-state (Port unselected)

Tri-state

0

1

Tri-state (Port unselected)

Tri-state

0

Address/Data input

Input

1

0

Data output

Output

L6260

17/30

相關PDF資料 |

PDF描述 |

|---|---|

| L6561I | 0.7 A POWER FACTOR CONTROLLER, PDIP8 |

| L6561C | 0.7 A POWER FACTOR CONTROLLER, PDIP8 |

| L6561DI | 0.7 A POWER FACTOR CONTROLLER, PDSO8 |

| L6561DC | 0.7 A POWER FACTOR CONTROLLER, PDSO8 |

| L6562AD | 0.8 A POWER FACTOR CONTROLLER, PDSO8 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| L6261 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Servo/Spindle Motor Controller/Driver |

| L62622.6 | 制造商:STMicroelectronics 功能描述: |

| L6268 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:12V DISK DRIVE SPINDLE & VCM, POWER & CONTROL “COMBO” |

| L6269 | 制造商:STMicroelectronics 功能描述:L6269 - Trays |

| L6269TR | 制造商:STMicroelectronics 功能描述:12V SMART POWER COMBO - Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。