- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377798 > LXT332 (Digital Data Communications GmbH) 3941 PDF資料下載

參數(shù)資料

| 型號(hào): | LXT332 |

| 廠商: | Digital Data Communications GmbH |

| 英文描述: | 3941 |

| 中文描述: | 雙T1/E1線路接口單元與水晶無衰減 |

| 文件頁(yè)數(shù): | 9/32頁(yè) |

| 文件大?。?/td> | 777K |

| 代理商: | LXT332 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)

L1

eììè

/;7êê 'XDO 7ì(ì /LQH ,QWHUIDFH 8QLW ZLWK &U\VWDOeOHVV -LWWHU $WWHQXDWLRQ

ì

RCLK0

DO

Receive Clock - Port 0.

This clock is recovered from the input signal. Under

Loss of Signal (LOS) conditions, this output is derived from MCLK.

Transmit All Ones Enable - Port 0.

When TAOS is High and RLOOP is

Low, the TPOS/TNEG or TDATA input is ignored and port 0 transmits a

stream of ones at the TCLK frequency. If TCLK is not provided, the MCLK

input is used as the transmit reference.

Line Length Equalizer Inputs - Port 0.

This pins determine the shape and

amplitude of the transmit pulse.

TAOS0

DI

ê

é

è

ìí

ìì

LEN20

LEN10

LEN00

MCLK

DI

DI

DI

DI

ì

Master Clock.

The master clock (1.544 MHz for T1, 2.048 MHz for E1) input

must be independent, free-running, continuously active and jitter free for

receiver operation. Since the transceivers derive their RCLK timing from the

MCLK input on Loss of Signal (LOS), MCLK cannot be derived from RCLK.

Ground.

Ground return for power supply VCC.

Transmit Tip and Ring - Port 0.

The tip and ring pins for each port are dif-

ferential driver outputs designed to drive a 35 - 200

load. Line matching

resistors and transformers can be selected to give the desired pulse height. See

Figures 13 through 15.

Ground.

Ground return for power supply TVCC0.

+ 5 volt

power supply input for the port 0 transmit driver. TVCC0 must not

vary from TVCC1 or VCC by more than ± 0.3 V.

Driver Fail Monitor.

This signal goes High to indicate a driver output short

in one or both ports.

Remote Loopback Enable - Port 0.

When RLOOP = 1, the port 0 clock and

data inputs from the framer are ignored and the data received from the twisted-

pair line is transmitted back onto the line at the RCLK frequency.

(LLOOP0

must be Low for RLOOP0 to occur.)

Loss of Signal - Port 0.

LOS goes High when 175 consecutive spaces have

been detected. LOS returns Low when the received signal reaches a mark den-

sity of 12.5% (determined by receipt of four marks with a sliding 32-bit period

with no more than 15 consecutive zeros). Received marks are output on

RPOS/RNEG or RDATA even when LOS is High.

Receive Tip and Ring - Port 0.

RTIP and RRING comprise the receive line

interface. This input pair should be connected to the line through a center-

tapped 1:2 transformer.

Local Loopback Enable - Port 0.

When LLOOP is High, the RTIP/RRING

inputs from the port 0 line are disconnected and the transmit data inputs are

routed back into the receive inputs (through JA if enabled).

(RLOOP0 must

be Low for LLOOP0 to occur.)

Receive Tip and Ring - Port 1.

RTIP and RRING comprise the receive line

interface. This input pair should be connected to the line through a center-

tapped 1:2 transformer.

ìì

ìê

ìé

ì

GND

TTIP0

TRING0

–

AO

AO

ìè

ì

TGND0

TVCC0

–

ìí

AI

ì

ì

DFM

DO

ìê

ì

RLOOP0

DI

ìé

í

LOS0

DO

ìè

ì

ì

RTIP0

RRING0

AI

AI

ì

ê

LLOOP0

DI

ì

ì

é

è

RRING1

RTIP1

AI

AI

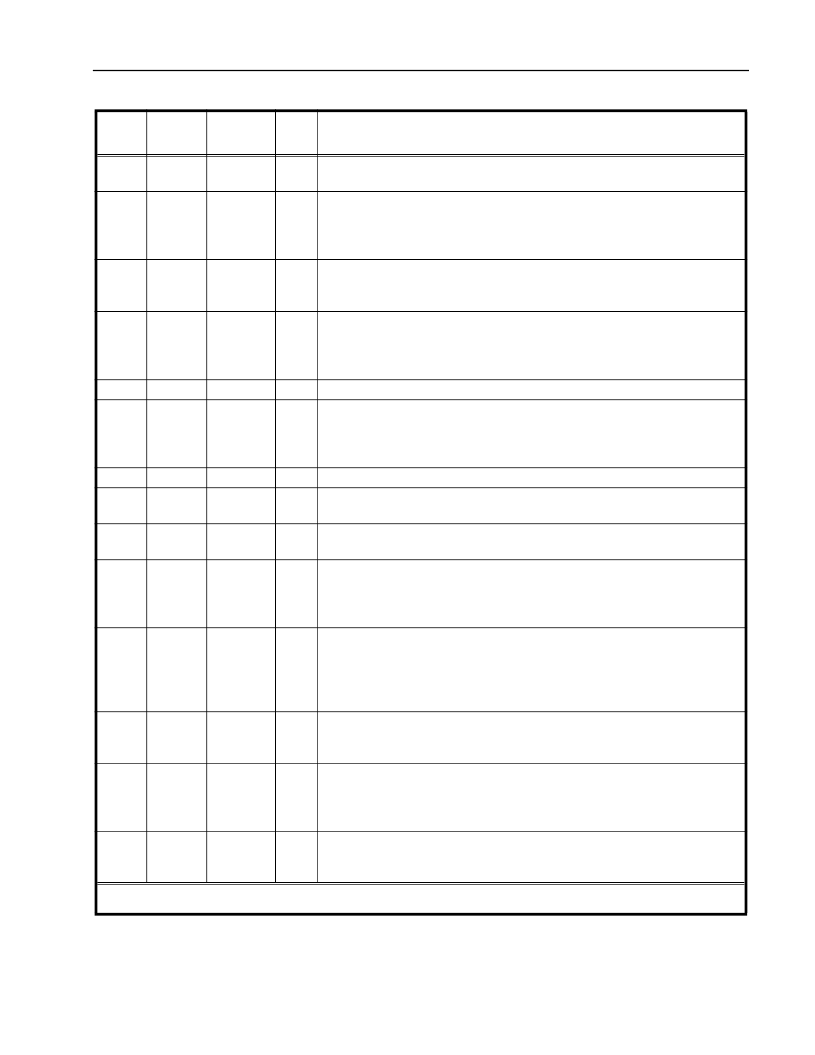

7DEOH ê +DUGZDUH 0RGH 3LQ DQG %LSRODU +DUGZDUH 0RGH 3LQ 'HVFULSWLRQV

ì

¤ FRQWLQXHG

3LQ

4)3

3LQ

3/&&

6\PERO

,2

'HVFULSWLRQ

ì 7DEOH é GHVFULEHV WKH SLQV XVHG LQ 8QLSRODU +DUGZDUH 0RGH

', 'LJLWDO ,QSXWa '2 'LJLWDO 2XWSXWa ',2 'LJLWDO ,QSXW2XWSXWa $, $QDORJ ,QSXWa $2 $QDORJ 2XWSXW

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LXT334 | Quad Short Haul Transceiver with Clock Recovery |

| LXT335 | Quad Short Haul PCM Analog Interface |

| LXT350 | Integrated T1/E1 S/H Transceivers With Crystal-less Jitter Attenuation |

| LXT350QE | Integrated T1/E1 S/H Transceivers With Crystal-less Jitter Attenuation |

| LXT351 | T1/E1 Short Haul Transceiver with Crystal-less Jitter Attenuation |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LXT332PE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Line Interface |

| LXT332QE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Line Interface |

| LXT334 | 制造商:LVL1 制造商全稱:LVL1 功能描述:Quad Short Haul Transceiver with Clock Recovery |

| LXT334&LXT304A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LXT334 & LXT304A - LXT334 & LXT304A ?Low Cost & High Performance Quad E1 Interface Solution |

| LXT335 | 制造商:LVL1 制造商全稱:LVL1 功能描述:Quad Short Haul PCM Analog Interface |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。