- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377801 > M13S2561616A-5TG (ELITE SEMICONDUCTOR MEMORY TECHNOLOGY INC) 4M x 16 Bit x 4 Banks Double Data Rate SDRAM PDF資料下載

參數(shù)資料

| 型號: | M13S2561616A-5TG |

| 廠商: | ELITE SEMICONDUCTOR MEMORY TECHNOLOGY INC |

| 元件分類: | DRAM |

| 英文描述: | 4M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| 中文描述: | 16M X 16 DDR DRAM, 0.75 ns, PDSO66 |

| 封裝: | 0.400 X 875 INCH, 0.65 MM PITCH, LEAD FREE, TSOP2-66 |

| 文件頁數(shù): | 7/48頁 |

| 文件大?。?/td> | 1232K |

| 代理商: | M13S2561616A-5TG |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

ES MT

M13S2561616A

Elite Semiconductor Memory Technology Inc.

Publication Date : Jul. 2007

Revision : 1.3 7/48

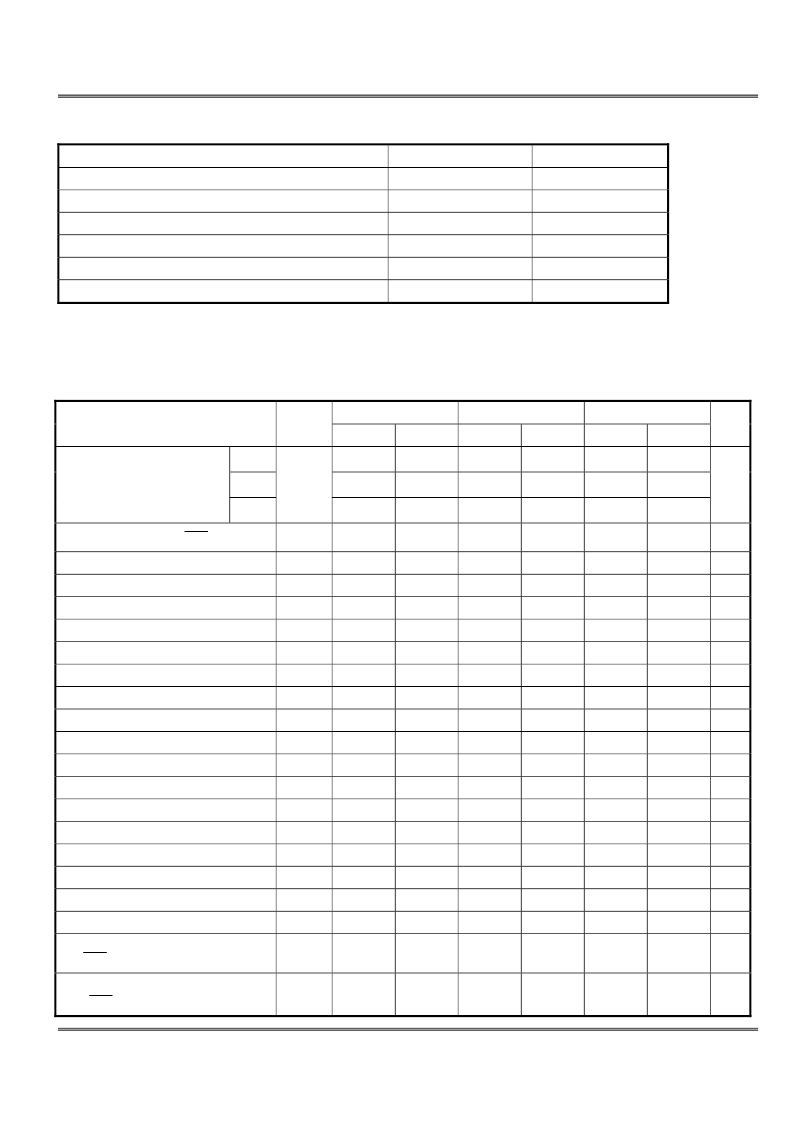

AC Operating Test Conditions

Parameter

Value

Unit

Input reference voltage for clock (V

REF

)

0.5*V

DDQ

V

Input signal maximum peak swing

1.5

V

Input signal minimum slew rate

1.0

V/ns

Input levels (V

IH

/V

IL

)

V

REF

+0.31/V

REF

-0.31

V

Input timing measurement reference level

V

REF

V

Output timing reference level

V

TT

V

AC Timing Parameter & Specifications

(V

DD

= 2.3V~2.7V, V

DDQ

=2.3V~2.7V, T

A

=0

C

(V

DD

= 2.6V~2.8V, V

DDQ

=2.6V~2.8V, T

A

=0

C

°

°

~ 70

C

~70

C

°

°

)

(only for speed -4) )

-4

-5

-6

Parameter

Symbol

min

max

min

max

min

max

CL2

7.5

10

7.5

10

7.5

12

CL2.5

5

10

5

10

6

12

Clock Period

CL3

t

CK

4.0

10

5.0

10

6.0

10

ns

Access time from CLK/CLK

t

AC

-0.75

+0.75

-0.75

+0.75

+0.75

+0.75

ns

CLK high-level width

t

CH

0.45

0.55

0.45

0.55

0.45

0.55

t

CK

CLK low-level width

t

CL

0.45

0.55

0.45

0.55

0.45

0.55

t

CK

Data strobe edge to clock edge

t

DQSCK

-0.55

+0.55

-0.55

+0.55

-0.6

+0.6

ns

Clock to first rising edge of DQS delay

t

DQSS

0.9

1.1

0.85

1.15

0.85

1.15

t

CK

Data-in and DM setup time (to DQS)

t

DS

0.6

-

0.6

-

0.6

-

ns

Data-in and DM hold time (to DQS)

t

DH

0.45

-

0.45

-

0.45

-

ns

DQ and DM input pulse width (for each input)

t

DIPW

1.75

-

1.75

-

1.75

ns

Input setup time (fast slew rate)

t

IS

0.75

-

0.75

-

0.75

-

ns

Input hold time (fast slew rate)

t

IH

0.75

-

0.75

-

0.75

-

ns

Input setup time (slow slew rate)

t

IS

0.8

-

0.8

-

0.8

-

ns

Input hold time (slow slew rate)

t

IH

0.8

-

0.8

-

0.8

-

ns

Control and Address input pulse width

t

IPW

2.2

-

2.2

-

2.2

-

ns

DQS input high pulse width

t

DQSH

0.35

-

0.35

-

0.35

-

t

CK

DQS input low pulse width

t

DQSL

0.35

-

0.35

-

0.35

-

t

CK

DQS falling edge to CLK rising-setup time

t

DSS

0.2

-

0.2

-

0.2

-

t

CK

DQS falling edge from CLK rising-hold time

t

DSH

0.2

-

0.2

-

0.2

t

CK

Data strobe edge to output data edge

t

DQSQ

-

0.40

-

0.40

-

0.45

ns

Data-out high-impedance window from

CLK/

CLK

t

HZ

-0.7

+0.7

-0.7

+0.7

-0.7

+0.7

ns

Data-out low-impedance window from

CLK/CLK

t

LZ

-0.7

+0.7

-0.7

+0.7

-0.7

+0.7

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M13S2561616A-6TG | 4M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S256328A | 2M x 32 Bit x 4 Banks Double Data Rate SDRAM |

| M13S32321A | 256K x 32 Bit x 4 Banks Double Data Rate SDRAM |

| M13S64164A-6BG | 1M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S64164A | 1M x 16 Bit x 4 Banks Double Data Rate SDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M13S2561616A-5TIG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:4M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S2561616A-6BG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:4M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S2561616A-6BIG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:4M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S2561616A-6TG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:4M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S2561616A-6TIG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:4M x 16 Bit x 4 Banks Double Data Rate SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。