- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄229296 > M48Z12-70PC6 (STMICROELECTRONICS) 2K X 8 NON-VOLATILE SRAM MODULE, 70 ns, PDIP24 PDF資料下載

參數(shù)資料

| 型號: | M48Z12-70PC6 |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | SRAM |

| 英文描述: | 2K X 8 NON-VOLATILE SRAM MODULE, 70 ns, PDIP24 |

| 封裝: | 0.600 INCH, ROHS COMPLIANT, CAPHAT, PLASTIC, DIP-24 |

| 文件頁數(shù): | 20/21頁 |

| 文件大小: | 177K |

| 代理商: | M48Z12-70PC6 |

Operation modes

M48Z02, M48Z12

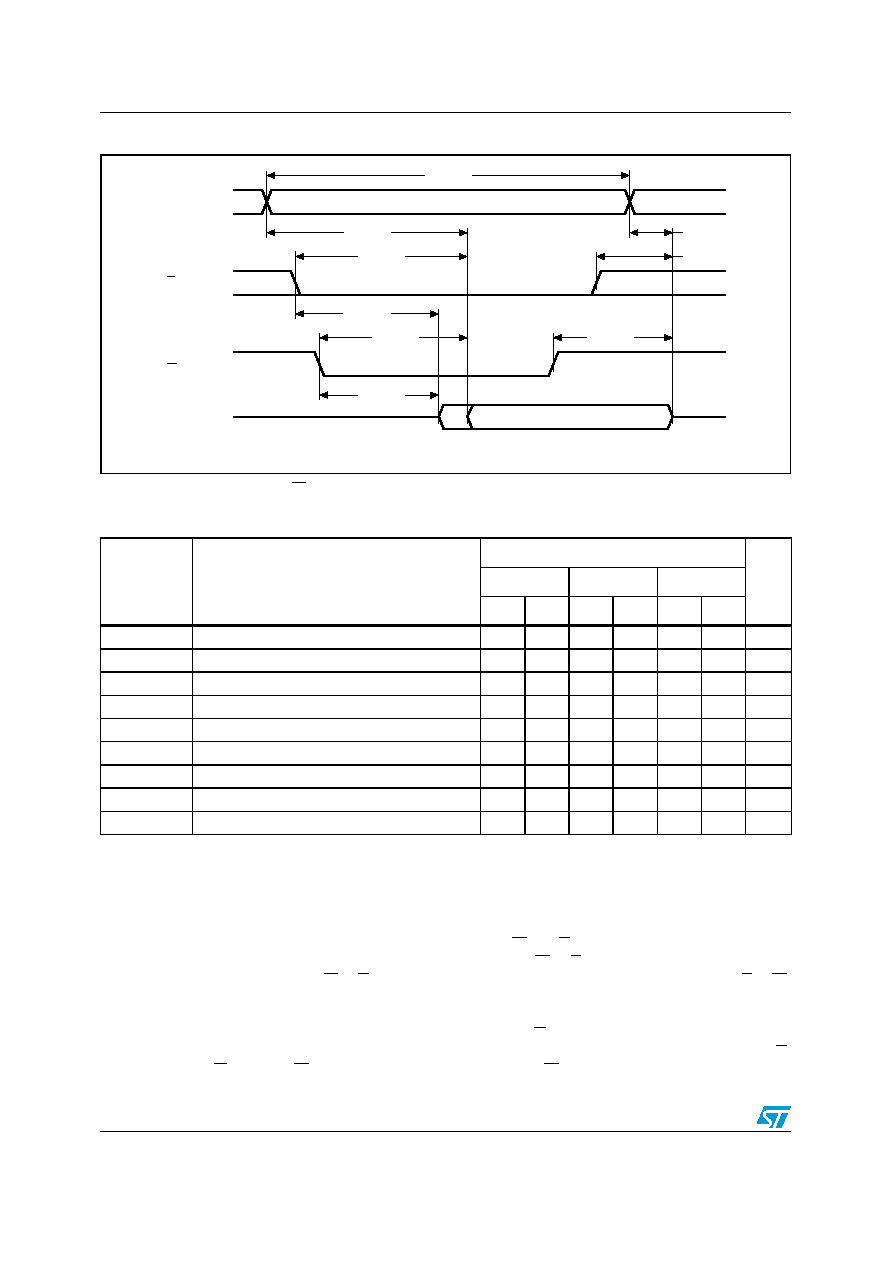

Figure 4.

Read mode AC waveforms

Note:

WRITE enable (W) = high.

Table 3.

Read mode AC characteristics

2.2

Write mode

The M48Z02/12 is in the WRITE mode whenever W and E are active. The start of a WRITE

is referenced from the latter occurring falling edge of W or E. A WRITE is terminated by the

earlier rising edge of W or E. The addresses must be held valid throughout the cycle. E or W

must return high for a minimum of tEHAX from chip enable or tWHAX from WRITE enable prior

to the initiation of another READ or WRITE cycle. Data-in must be valid tDVWH prior to the

end of WRITE and remain valid for tWHDX afterward. G should be kept high during WRITE

cycles to avoid bus contention; although, if the output bus has been activated by a low on E

and G, a low on W will disable the outputs tWLQZ after W falls.

Symbol

Parameter(1)

1.

Valid for ambient operating temperature: TA = 0 to 70°C or –40 to 85°C; VCC = 4.75 to 5.5 V or 4.5 to 5.5 V (except where

noted).

M48Z02/M48Z12

Unit

–70

–150

–200

Min

Max

Min

Max

Min

Max

tAVAV

READ cycle time

70

150

200

ns

tAVQV

Address valid to output valid

70

150

200

ns

tELQV

Chip enable low to output valid

70

150

200

ns

tGLQV

Output enable low to output valid

35

75

80

ns

tELQX

Chip enable low to output transition

5

10

ns

tGLQX

Output enable low to output transition

5

ns

tEHQZ

Chip enable high to output Hi-Z

25

35

40

ns

tGHQZ

Output enable high to output Hi-Z

25

35

40

ns

tAXQX

Address transition to output transition

10

5

ns

AI01330

tAVAV

tAVQV

tAXQX

tELQV

tELQX

tEHQZ

tGLQV

tGLQX

tGHQZ

VALID

A0-A10

E

G

DQ0-DQ7

VALID

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT48V8M16LFF4-10XT | 8M X 16 SYNCHRONOUS DRAM, 7 ns, PBGA54 |

| MT55L256V36PT-6 | 256K X 36 ZBT SRAM, 3.5 ns, PQFP100 |

| MT5C2561EC-45IT | 256K X 1 STANDARD SRAM, 45 ns, CQCC28 |

| M378T3253FG0-CE6 | 32M X 64 DDR DRAM MODULE, 0.45 ns, DMA240 |

| M93C06-DS3TG | 16 X 16 MICROWIRE BUS SERIAL EEPROM, PDSO8 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M48Z12-70PC6TR | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:5V, 16 Kbit (2Kb x 8) ZEROPOWER SRAM |

| M48Z128 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:1 Mbit 128Kb x8 ZEROPOWER SRAM |

| M48Z128_10 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:5.0 V or 3.3 V, 1 Mbit (128 Kbit x 8) ZEROPOWER? SRAM |

| M48Z128-120CS1 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:1 Mbit 128Kb x8 ZEROPOWER SRAM |

| M48Z128-120PM1 | 功能描述:NVRAM 1M (128Kx8) 120ns RoHS:否 制造商:Maxim Integrated 數(shù)據(jù)總線寬度:8 bit 存儲容量:1024 Kbit 組織:128 K x 8 接口類型:Parallel 訪問時間:70 ns 電源電壓-最大:5.5 V 電源電壓-最小:4.5 V 工作電流:85 mA 最大工作溫度:+ 70 C 最小工作溫度:0 C 封裝 / 箱體:EDIP 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。