- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄180472 > MACH131SP-7YC (LATTICE SEMICONDUCTOR CORP) High-Performance EE CMOS Programmable Logic PDF資料下載

參數(shù)資料

| 型號(hào): | MACH131SP-7YC |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | PLD |

| 英文描述: | High-Performance EE CMOS Programmable Logic |

| 中文描述: | EE PLD, 7.5 ns, PQFP100 |

| 封裝: | PLASTIC, QFP-100 |

| 文件頁(yè)數(shù): | 42/47頁(yè) |

| 文件大小: | 1200K |

| 代理商: | MACH131SP-7YC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)當(dāng)前第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)

MACH 1 & 2 Families

47

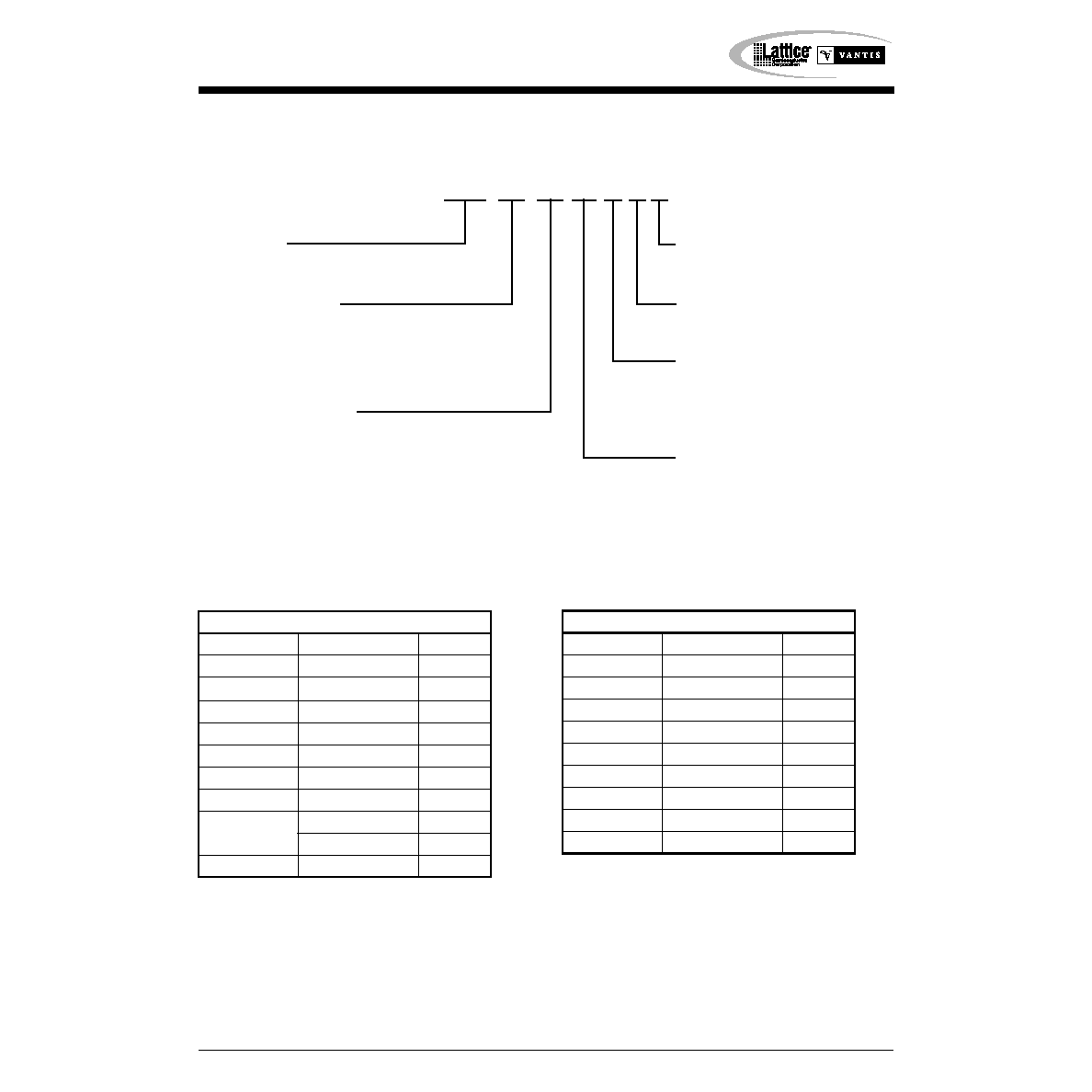

ORDERING INFORMATION

Lattice/Vantis programmable logic products are available with several ordering options. The order number (Valid Combination) is

formed by a combination of:

Valid Combinations

The Valid Combinations list congurations planned to be

supported in volume for this device. Consult the local Lattice/

Vantis sales ofce to conrm availability of specic valid

combinations and to check on newly released combinations.

Note:

1. All MACH devices are dual-marked with both Commercial and Industrial grades. The Industrial grade is slower, i.e.

MACH131SP-5YC-7YI

SP

FAMILY TYPE

MACH = Macro Array CMOS High-Density

MACH

131

Y

C

MACROCELL DENSITY

111

= 32 Macrocells, 32 I/Os

131

= 64 Macrocells, 64 I/Os

211

= 64 Macrocells, 32 I/Os

221

= 96 Macrocells, 48 I/Os

231

= 128 Macrocells, 64 I/Os

PRODUCT DESIGNATION

SP

= JTAG-compatible, In-system Programmable

OPERATING CONDITIONS

C

= Commercial (0

°C to +70°C)

I

= Industrial (-40

°C to +85°C)

PACKAGE TYPE

J

= Plastic Leaded Chip Carrier

(PLCC)

V

= Thin Quad Flat Pack (TQFP)

Y

= Plastic Quad Flat Pack (PQFP)

SPEED

-5 = 5.0 or 5.5 ns tPD

-6 = 6.0 ns tPD

-7 = 7.5 ns tPD

-10 = 10 ns tPD

-12 = 12 ns tPD

-14 = 14 ns tPD

-15 = 15 ns tPD

-18 = 18 ns tPD

-5

PROGRAMMING DESIGNATOR

Blank = Initial Algorithm

/1

= First Revision

Valid Combinations – Commercial

MACH111

-5, -7, -10, -12, -15

JC, VC

MACH111SP

-5, -7, -10, -12, -15

JC, VC

MACH131

-5, -7, -10, -12, -15

JC/1

MACH131SP

-5, -7, -10, -12, -15

VC, YC

MACH211

-7, -10, -12, -15

JC, VC

MACH211SP

-6, -7, -10, -12, -15

JC, VC

MACH221

-7, -10, -12, -15

JC

MACH221SP

-7, -10, -12, -15

YC

MACH231

-6, -7

JC

-10, -12, -15

JC/1

MACH231SP

-10, -12, -15

VC, YC

Valid Combinations – Industrial

MACH111

-7, -10, -12, -14, -18

JI

MACH111SP

-7, -10, -12, -14, -18

JI

MACH131

-7, -10, -12, -14, -18

JI/1

MACH131SP

-7, -10, -12, -14, -18

YI

MACH211

-10, -12, -14, -18

JI

MACH211SP

-10, -12, -14, -18

JI

MACH221

-10, -12, -14, -18

JI

MACH221SP

-10, -12, -14, -18

YI

MACH231

-12, -14, -18

JI/1

MACH231SP

-12, -14, -18

YI

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MACH1 | High-Performance EE CMOS Programmable Logic |

| MACH210A-10JC | High-Density EE CMOS Programmable Logic |

| MACH210A-10VC | High-Density EE CMOS Programmable Logic |

| MACH210A-12JC | High-Density EE CMOS Programmable Logic |

| MACH210A-12VC | High-Density EE CMOS Programmable Logic |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MACH131SP-7YI | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 HI PERF EE CMOS PLD RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| MACH210 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:44 pin QFP socket/28 pin DIP 0.6” plug |

| MACH210-12 | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:High-Density EE CMOS Programmable Logic |

| MACH21012JC | 制造商:AMD 功能描述:* |

| MACH210-12JC | 制造商:Advanced Micro Devices 功能描述:COMPLEX-EEPLD, 64-CELL, 12NS PROP DELAY, 44 Pin, Plastic, PLCC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。