- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377905 > MB89374 (Fujitsu Limited) Data Link Controller (DLC)(數(shù)據(jù)鏈接控制器) PDF資料下載

參數(shù)資料

| 型號: | MB89374 |

| 廠商: | Fujitsu Limited |

| 英文描述: | Data Link Controller (DLC)(數(shù)據(jù)鏈接控制器) |

| 中文描述: | 數(shù)據(jù)鏈路控制器(金剛石)(數(shù)據(jù)鏈接控制器) |

| 文件頁數(shù): | 6/45頁 |

| 文件大小: | 328K |

| 代理商: | MB89374 |

第1頁第2頁第3頁第4頁第5頁當(dāng)前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁

6

MB89374

(Continued)

(Continued)

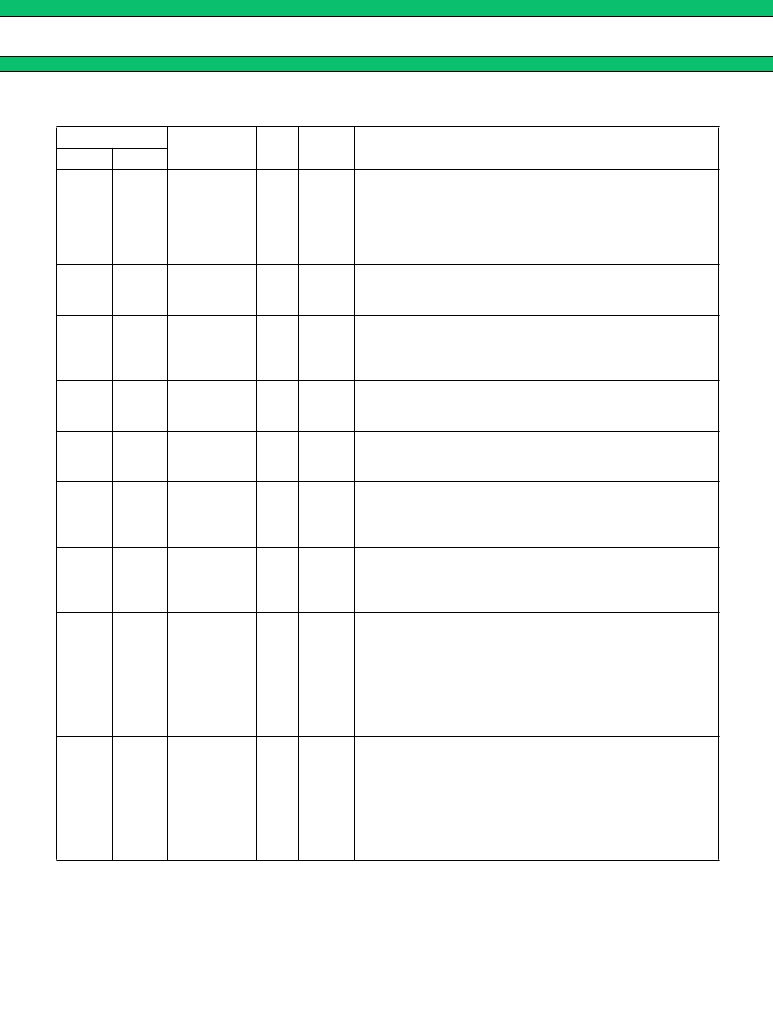

Pin No.

DIP

Symbol

I/O

Level*

Description

QFP

5

24

WR#/R/W#

I

—

Write or read/write pin:

This pin serves as the WR# input pin in the MBL8086/88

mode. A LOW level is input to this pin when writing to the

registers in the DLC. This pin serves as the R/W# input pin

in the GMICRO

mode. It determines the data direction when

accessing the registers in the DLC.

Chip-select pin:

A LOW level is input to this pin when accessing the registers

in the DLC.

CPU-interface mode-setting pin:

This pin is set to the GMICRO mode when the input level is

LOW, and to the MBL8086/88 mode when the input level is

HIGH. The pin input level must be fixed to LOW or HIGH.

6

26

CS#

I

—

2

21

FORMAT#

I

—

13 to

20

33 to

36,

38 to 41

D7 to D0

I/O

Hi-Z

Data-bus (tristate) pins:

These pins are used to input and output 8-bit data.

7 to 11 27 to 31

A4 to A0

I

—

Address pins:

These pins are used to input addresses to select the

registers in the DLC.

Interrupt-request pin:

This pin is used to generate HIGH interrupt requests by

using bits other than the BRG2OUT bit of the BRG2 status

register (B2SR) as interrupt trigger bits.

Interrupt-request pin:

This pin is used to generate HIGH interrupt requests by

using the BRG2OUT bit of the BRG2 status register (B2SR)

as the interrupt trigger bit.

Receive DMA-request or port-output 3 pin:

The receive DMA-request pin or port-output pin is selected

by the RxD/I bit of the receive interrupt enable register

(RxIER). If this pin is used as the RxDRQ pin, it outputs a

HIGH level to request DMA transfer of receive data. If this

pin is used as the PO3 pin, it outputs a HIGH level when the

PO3 bit of the port register (PORTR) is 1, and a LOW level

when the PO3 bit is 0.

Transmit DMA-request or port-output 2 pin:

The transmit DMA-request pin or port-output pin is selected

by the TxD/I bit of the transmit interrupt enable register

(TxIER). If this pin is used as the TxDRQ pin, it outputs a

HIGH level to request the DMA transfer of transmit data. If

this pin is used as the PO2 pin, it outputs a HIGH level when

the PO2 bit of the port register (PORTR) is 1, and a LOW

level when the PO2 bit is 0.

35

10

IRQ

O

L

37

12

IRQT

O

L

39

15

R

X

DRQ/PO3

O

L

38

14

T

X

DRQ/PO2

O

L

Signals suffixed by the symbol # are negative logic.

* :Pin output level when reset

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB89470 | 8-bit Proprietary Microcontroller |

| MB89475 | 8-bit Proprietary Microcontroller |

| MB89475PFM | 8-bit Proprietary Microcontroller |

| MB89475PFV | 8-bit Proprietary Microcontroller |

| MB89475P-SH | 8-bit Proprietary Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB89470 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:8-bit Proprietary Microcontroller |

| MB89475 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:8-bit Proprietary Microcontroller |

| MB89475PFM | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:8-bit Proprietary Microcontroller |

| MB89475PFV | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:8-bit Proprietary Microcontroller |

| MB89475P-SH | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:8-bit Proprietary Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。