- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377941 > MBM29DL640E90TN (FUJITSU LTD) 64 M (8 M X 8/4 M X 16) BIT Dual Operation PDF資料下載

參數(shù)資料

| 型號: | MBM29DL640E90TN |

| 廠商: | FUJITSU LTD |

| 元件分類: | DRAM |

| 英文描述: | 64 M (8 M X 8/4 M X 16) BIT Dual Operation |

| 中文描述: | 4M X 16 FLASH 3V PROM, 90 ns, PDSO48 |

| 封裝: | PLASTIC, TSOP1-48 |

| 文件頁數(shù): | 12/71頁 |

| 文件大?。?/td> | 913K |

| 代理商: | MBM29DL640E90TN |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當(dāng)前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁

MBM29DL640E

80/90/12

12

(Continued)

*1:This command is valid during Fast Mode.

*2:This command is valid while RESET

=

V

ID

.

*3:This command is valid during Hi-ROM mode.

*4:The data “00h” is also acceptable.

Address bits A

21

to A

11

=

X

=

“H” or “L” for all address commands except or Program Address (PA) , Sector

Address (SA) , Bank Address (BA) and Sector Group Address (SPA) .

2.

Bus operations are defined in Tables 2 and 3.

3.

RA

=

Address of the memory location to be read

PA

=

Address of the memory location to be programmed

Addresses are latched on the falling edge of the write pulse.

SA

=

Address of the sector to be erased. The combination of A

21

, A

20

, A

19

, A

18

, A

17

, A

16

, A

15

, A

14

, A

13

and

A

12

will uniquely select any sector.

BA

=

Bank Address. Address setted by A

21

, A

20

, A

19

will select Bank A, Bank B, Bank C and Bank D.

4.

RD

=

Data read from location RA during read operation.

PD

=

Data to be programmed at location PA. Data is latched on the falling edge of write pulse.

5.

SPA

=

Sector group address to be protected. Set sector group address and (A

6

, A

3

, A

2

, A

1

, A

0

)

=

(0, 0, 0, 1, 0) .

SD

=

Sector group protection verify data. Output 01h at protected sector group addresses and output

00h at unprotected sector group addresses.

6.

HRA

=

Address of the Hi-ROM area

Word Mode : 000000h to 00007Fh

Byte Mode : 000000h to 0000FFh

7.

HRBA

=

Bank Address of the Hi-ROM area (A

21

=

A

20

=

A

19

=

V

IL

)

8.

The system should generate the following address patterns:

Word Mode : 555h or 2AAh to addresses A

10

to A

0

Byte Mode : AAAh or 555h to addresses A

10

to A

0

, and A

-1

9.

Both Read/Reset commands are functionally equivalent, resetting the device to the read mode.

Notes : 1.

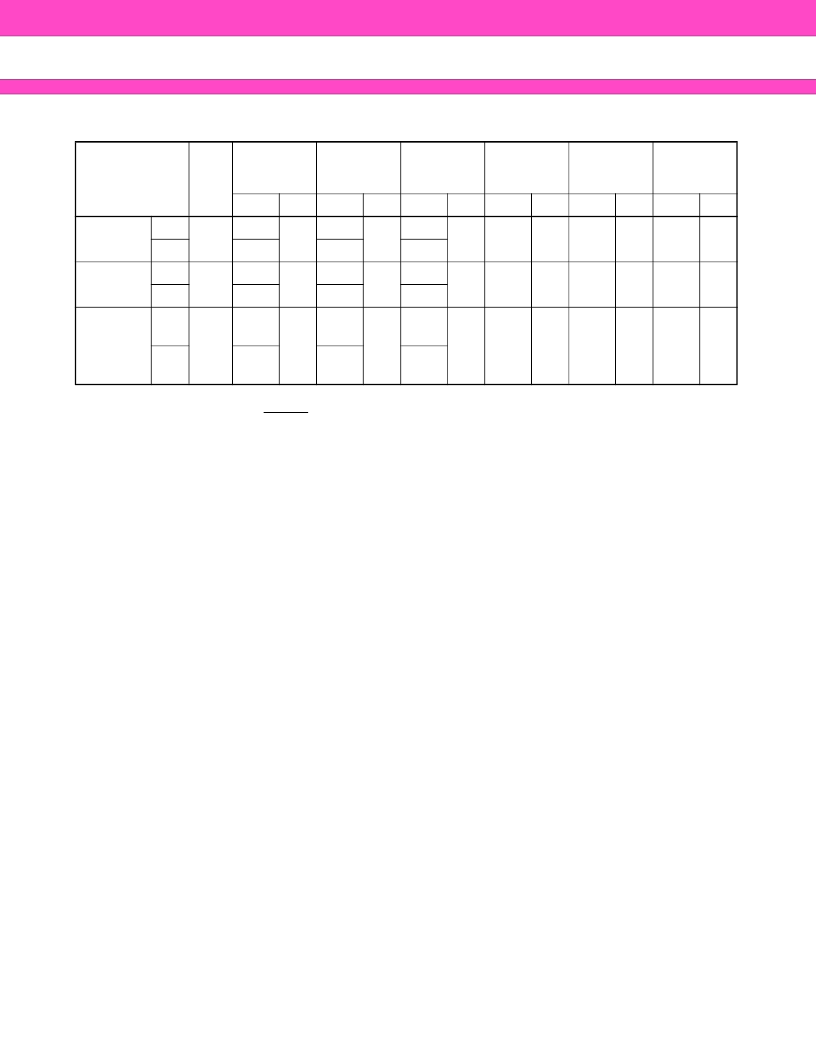

Command

Sequence

Bus

Write

Cy-

cles

Req’d

First Bus

Write Cycle

Second Bus

Write Cycle

Third Bus

Write Cycle

Fourth Bus

Read/Write

Cycle

Fifth Bus

Write Cycle

Sixth Bus

Write Cycle

Addr. Data Addr. Data Addr. Data Addr. Data Addr. Data Addr. Data

Hi-ROM

Entry

Word

3

555h

AAh

2AAh

55h

555h

88h

—

—

—

—

—

—

Byte

AAAh

555h

AAAh

Hi-ROM

Program *

3

Word

4

555h

AAh

2AAh

55h

555h

A0h

(HRA)

PA

PD

—

—

—

—

Byte

AAAh

555h

AAAh

Hi-ROM

Exit *

3

Word

4

555h

AAh

2AAh

55h

(HRBA)

555h

90h

XXXh

00h

—

—

—

—

Byte

AAAh

555h

(HRBA)

AAAh

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MBM29DL640E90TR | 64 M (8 M X 8/4 M X 16) BIT Dual Operation |

| MBM29DL64DF | FLASH MEMORY CMOS 64 M (8 M X 8/4 M X 16) BIT |

| MBM29DL64DF-70 | FLASH MEMORY CMOS 64 M (8 M X 8/4 M X 16) BIT |

| MBM29DL64DF70PBT | FLASH MEMORY CMOS 64 M (8 M X 8/4 M X 16) BIT |

| MBM29DL64DF70TN | FLASH MEMORY CMOS 64 M (8 M X 8/4 M X 16) BIT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MBM29DL640E90TN-LE1 | 制造商:Spansion 功能描述: |

| MBM29DL640E90TR | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:64 M (8 M X 8/4 M X 16) BIT Dual Operation |

| MBM29DL64DF | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:FLASH MEMORY CMOS 64 M (8 M X 8/4 M X 16) BIT |

| MBM29DL64DF-70 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:FLASH MEMORY CMOS 64 M (8 M X 8/4 M X 16) BIT |

| MBM29DL64DF70PBT | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:FLASH MEMORY CMOS 64 M (8 M X 8/4 M X 16) BIT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。