- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371014 > MC145181 (Motorola, Inc.) Dual 550/60MHz PLL Frequency Synthesizers with DACs and Voltage Multipliers(帶DACs和電壓乘法器的雙550/60MHzPLL頻率合成器) PDF資料下載

參數(shù)資料

| 型號: | MC145181 |

| 廠商: | Motorola, Inc. |

| 英文描述: | Dual 550/60MHz PLL Frequency Synthesizers with DACs and Voltage Multipliers(帶DACs和電壓乘法器的雙550/60MHzPLL頻率合成器) |

| 中文描述: | 雙550/60MHz鎖相環(huán)頻率合成器的DAC和電壓倍增器(帶數(shù)模轉(zhuǎn)換器和電壓乘法器的雙550/60MHzPLL頻率合成器) |

| 文件頁數(shù): | 34/71頁 |

| 文件大小: | 907K |

| 代理商: | MC145181 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁當(dāng)前第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁

MC145181

34

MOTOROLA RF/IF DEVICE DATA

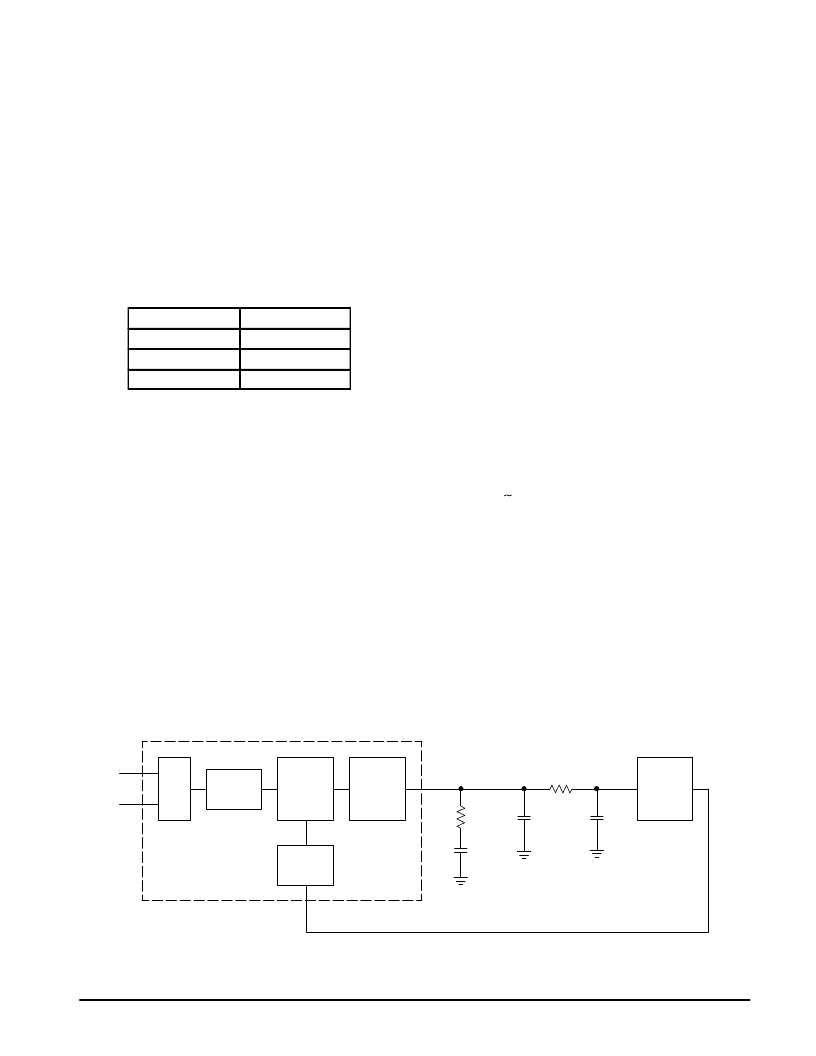

7B. MAIN LOOP FILTER DESIGN — CONVENTIONAL

The current output of the charge pump allows the loop

filter to be realized without the need of any active

components. The preferred topology for the filter is illustrated

in Figure 29.

The Ro/Co components realize the primary loop filter. Ca

is added to the loop filter to provide for reference sideband

suppression. If additional suppression is needed, the Rx/Cx

realizes an additional filter. In most applications, this will not

be necessary. If all components are used, this results in a

fourth order PLL, which makes analysis difficult. To simplify

this, the loop design will be treated as a second order loop

(Ro/Co), and additional guidelines are provided to minimize

the influence of the other components. If more rigorous

analysis is needed, mathematical/system simulation tools

should be used.

Component

Guideline

Ca

Rx

Cx

<0.1 x Co

>10 x Ro

<0.1 x Co

The focus of the design effort is to determine what the

loop’s natural frequency,

ω

o, should be. This is determined by

Ro, Co, Kp, Kv, and Nt. Because Kp, Kv, and Nt are given, it is

only necessary to calculate values for Ro and Co. There are

three considerations in selecting the loop bandwidth:

1. Maximum loop bandwidth for minimum tuning speed.

2. Optimum loop bandwidth for best phase noise

performance.

3. Minimum loop bandwidth for greatest reference

sideband suppression.

Usually a compromise is struck between these three

cases, however, for a fixed frequency application, minimizing

the tuning speed is not a critical parameter.

To specify the loop bandwidth for optimal phase noise

performance, an understanding of the sources of phase

noise in the system and the effect of the loop filter on them is

required. There are three major sources of phase noise in the

phase–locked loop — the crystal reference, the VCO, and

the loop contribution. The loop filter acts as a low–pass filter

to the crystal reference and the loop contribution. The loop

filter acts as a high–pass filter to the VCO with an in–band

gain equal to unity. The loop contribution includes the PLL IC,

as well as noise in the system; supply noise, switching noise,

etc. For this example, a loop contribution of 15 dB has been

selected.

The crystal reference and the VCO are characterized as

high–order 1/f noise sources. Graphical analysis is used to

determine the optimum loop bandwidth. It is necessary to

have noise plots from the manufacturers of both devices.

This method provides a straightforward approximation

suitable for quickly estimating the optimal bandwidth. The

loop contribution is characterized as white–noise or

low–order 1/f noise, given in the form of a noise factor which

combines all the noise effects into a single value. The phase

noise of the crystal reference is increased by the noise factor

of the PLL IC and related circuitry. It is further increased by

the total divide–by–N ratio of the loop. This is illustrated in

Figure 30. The point at which the VCO phase noise crosses

the amplified phase noise of the crystal reference is the point

of the optimum loop bandwidth. In the example of Figure 30,

the optimum bandwidth is approximately 15 kHz.

To simplify analysis further, a damping factor of 1 will be

selected. The normalized closed loop response is illustrated

in Figure 31 where the loop bandwidth is 2.5 times the loop

natural frequency (the loop natural frequency is the

frequency at which the loop would oscillate if it were

unstable). Therefore, the optimum loop bandwidth is

15 kHz/2.5 or 6.0 kHz (37.7 krads) with a damping

coefficient,

ζ

1. T(s) is the transfer function of the loop

filter.

where

Nt = Total PLL Divide Ratio — 8 x N

where (N = 25 ... 40),

Kv = VCO Gain – 2

π

Hz/V,

Kp = Phase Detector/Charge Pump Gain – A

= ( |IOH | + |IOL | ) / 4

π

.

Technically, Kv and Kp should be expressed in radian units

[Kv (rad/V), Kp (A/rad)]. Since the component design

equation contains the Kv x Kp term, the 2

π

cancels and the

value can be expressed as AHz/V (amp hertz per volt).

Figure 29. Loop Filter

Charge

Pump

Ph/Frq

Det

N Counter

Xtl

Osc

PLL

VCO

Co

Ca

Ro

Cx

Rx

R Counter

0

0

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC145193 | 1.1GHz PLL Frequency Synthesizer(1.1GHz PLL頻率合成器) |

| MC145202-1 | PLL Frequency Synthesizer(2.0GHz PLL頻率合成器) |

| MC145225 | Dual PLL Frequency Synthesizers With DACs and Voltage Multipliers(帶DACs和電壓乘法器的雙PLL頻率合成器) |

| MC145230 | Dual PLL Frequency Synthesizers With DACs and Voltage Multipliers(帶DACs和電壓乘法器的雙PLL頻率合成器) |

| MC14528BCL | Dual Monostable Multivibrator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC14518BCP | 功能描述:計數(shù)器移位寄存器 3-18V Dual BCD Up RoHS:否 制造商:Texas Instruments 計數(shù)器類型: 計數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| MC14518BCPG | 功能描述:計數(shù)器移位寄存器 3-18V Dual BCD Up RoHS:否 制造商:Texas Instruments 計數(shù)器類型: 計數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| MC14518BDW | 功能描述:計數(shù)器移位寄存器 3-18V Dual BCD Up RoHS:否 制造商:Texas Instruments 計數(shù)器類型: 計數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| MC14518BDWG | 功能描述:計數(shù)器移位寄存器 3-18V Dual BCD Up RoHS:否 制造商:Texas Instruments 計數(shù)器類型: 計數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| MC14518BDWR2 | 功能描述:計數(shù)器移位寄存器 3-18V Dual BCD Up RoHS:否 制造商:Texas Instruments 計數(shù)器類型: 計數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。