- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377972 > ML6431 (Fairchild Semiconductor Corporation) Genlocking Sync Generator with Digital Audio Clock for NTSC, PAL & VGA(用于NTSC, PAL & VGA數(shù)字式音頻同步時鐘發(fā)生器) PDF資料下載

參數(shù)資料

| 型號: | ML6431 |

| 廠商: | Fairchild Semiconductor Corporation |

| 英文描述: | Genlocking Sync Generator with Digital Audio Clock for NTSC, PAL & VGA(用于NTSC, PAL & VGA數(shù)字式音頻同步時鐘發(fā)生器) |

| 中文描述: | 同步鎖相同步發(fā)生器用于NTSC,PAL與數(shù)字音頻時鐘 |

| 文件頁數(shù): | 18/33頁 |

| 文件大?。?/td> | 384K |

| 代理商: | ML6431 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當(dāng)前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁

ML6430/ML6431

18

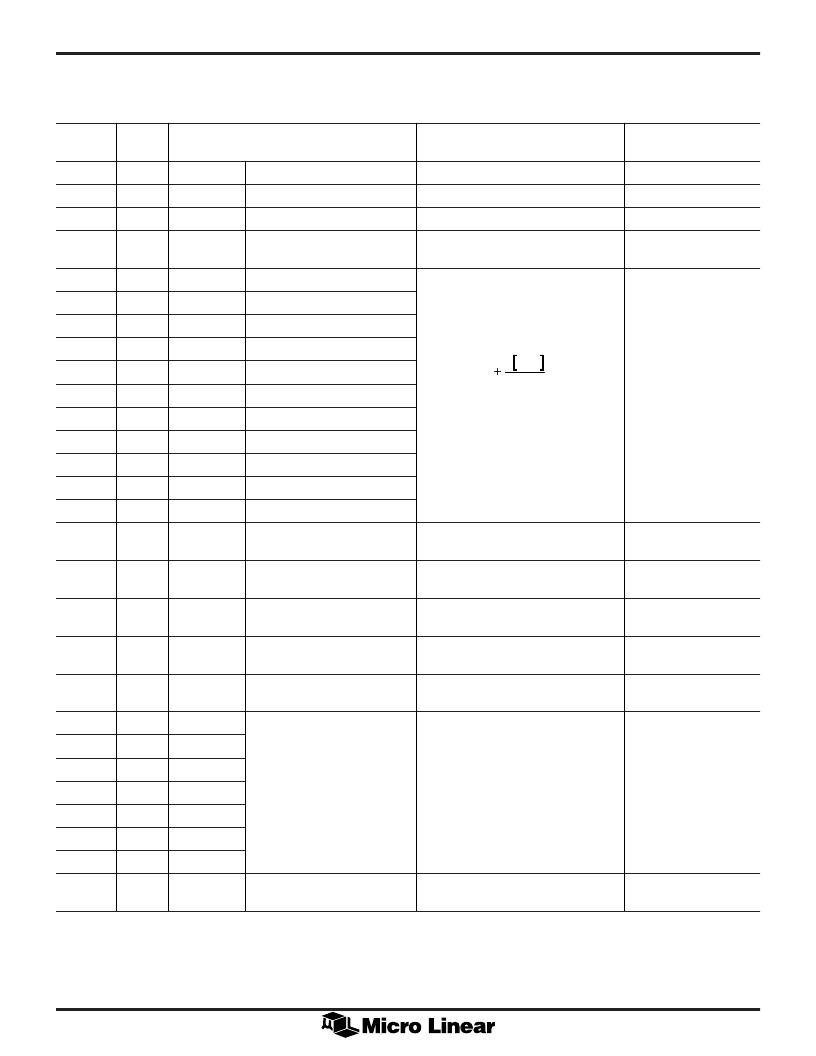

REGISTER

DATA

BIT

DESCRIPTION

VALUE RANGE

BIT CODE

RANGE

0

0

PulsePol 0

C

SYNC

Polarity

High Active-Low Active

0 or 1

0

1

PulsePol 1

H/V Blank Polarity

High Active-Low Active

0 or 1

0

2

PulsePol 2

S/B Clamp Polarity

High Active-Low Active

0 or 1

0

3

Clk 4X

Select 4X Clock

Low 1X Clock = 13.5MHz

High 4X Clock = 54MHz

0 or 1

1

0

Pixel0

Pix Counter Load Bit 0

1

1

Pixel1

Pix Counter Load Bit 1

1

2

Pixel2

Pix Counter Load Bit 2

1

3

Pixel3

Pix Counter Load Bit 3

2

0

Pixel4

Pix Counter Load Bit 4

2

1

Pixel5

Pix Counter Load Bit 5

2

2

Pixel6

Pix Counter Load Bit 6

2

3

Pixel7

Pix Counter Load Bit 7

3

0

Pixel8

Pix Counter Load Bit 8

3

1

Pixel9

Pix Counter Load Bit 9

3

2

Pixel10

Pix Counter Load Bit 10

3

3

Burst

Burst Gate Enable

Low = Back Porch Clamp

High = Burst Gate

0 or 1

4

0

CSyncRaw

(or C

SYNC

Regen)

Low = regenerated C

SYNC

High = raw C

SYNC

0 or 1

4

1

RawClamp

(or Clamp Regen)

Low = regenerated Clamp

High = raw Clamp

0 or 1

4

2

TTL Sync

TTL horizontal + vertical

Sync Input

Low = sync separator active

High = TTL horiz + vert sync input

0 or 1

4

3

WideBlank

(or Narrow)

Low = narrow blanking

High = wide blanking

0 or 1

5

0

HDelay0

5

1

HDelay1

5

2

HDelay2

5

3

HDelay3

6

0

HDelay4

6

1

HDelay5

6

2

HDelay6

6

3

Noise Gating 3/4 line lockout

Low = noise gating on

High = noise gating off

0 or 1

Numerical value taken as unsigned

binary. Actual no. of pixels is:

512

100

2

+

P

:

Do not vary pixel [10:0] by more than

±6% from nominal.

1024 > no. of pixels > 512 and

f

NOM

x 1.06 > f

NEW

> f

NOM

x 0.94

nom = ~011 0000 0000

max = 011 0011 0000

min = 010 1101 0000

H Delay parameter allows

moving the entire constellation

of output pulses relative to the

incoming H

SYNC

. Exception:

Sync Tip clamp may be

selected for delay or triggered

from incoming sync

depending on application.

7-bit Horizontal Delay parameter.

Values:

–64p< Hdly < 63p, p = 1/F

4XCLK

0000000 to 1111111:

0000000 means –64p

1111111 means +63p

1000000 means 0p

Table 10. ML6430 Register Map

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ML6440 | Multi-Standard 8-bit Adaptive Digital Input Comb Filter(多標準8位自適應(yīng)數(shù)字輸入組合濾波器) |

| ML6460 | CCIR656 NTSC Video Encoder(CCIR656標準NTSC視頻編碼器) |

| ML6509 | Active SCSI Terminator(SCSI系統(tǒng)的有源終端器) |

| ML6510 | Series Programmable Adaptive Clock Manager(系列可編程自適應(yīng)時鐘管理器) |

| ML6516244 | 16-Bit Buffer/Line Driver with 3-State Outputs(BiCMOS 16位緩沖器/線驅(qū)動器(三態(tài)輸出)) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ML6431CH | 制造商:Rochester Electronics LLC 功能描述: |

| ML6431CH WAF UP | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| ML643RAU111MLZ | 制造商:COILCRAFT 制造商全稱:Coilcraft lnc. 功能描述:High-Reliability Air Core Inductors |

| ML6440 | 制造商:MICRO-LINEAR 制造商全稱:MICRO-LINEAR 功能描述:Multi-Standard 8-bit Adaptive Digital Input Comb Filter |

| ML6440CH | 制造商:MICRO-LINEAR 制造商全稱:MICRO-LINEAR 功能描述:Multi-Standard 8-bit Adaptive Digital Input Comb Filter |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。