- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371134 > MPC106ARX83DG (MOTOROLA INC) PCI Bridge/Memory Controller PDF資料下載

參數(shù)資料

| 型號(hào): | MPC106ARX83DG |

| 廠商: | MOTOROLA INC |

| 元件分類: | 總線控制器 |

| 英文描述: | PCI Bridge/Memory Controller |

| 中文描述: | PCI BUS CONTROLLER, CBGA304 |

| 封裝: | 21 X 25 MM, 3.16 MM HEIGHT, 1.27 MM PITCH, CERAMIC, BGA-304 |

| 文件頁數(shù): | 27/28頁 |

| 文件大小: | 158K |

| 代理商: | MPC106ARX83DG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當(dāng)前第27頁第28頁

MPC106 PCI Bridge/Memory Controller Hardware Specifications

27

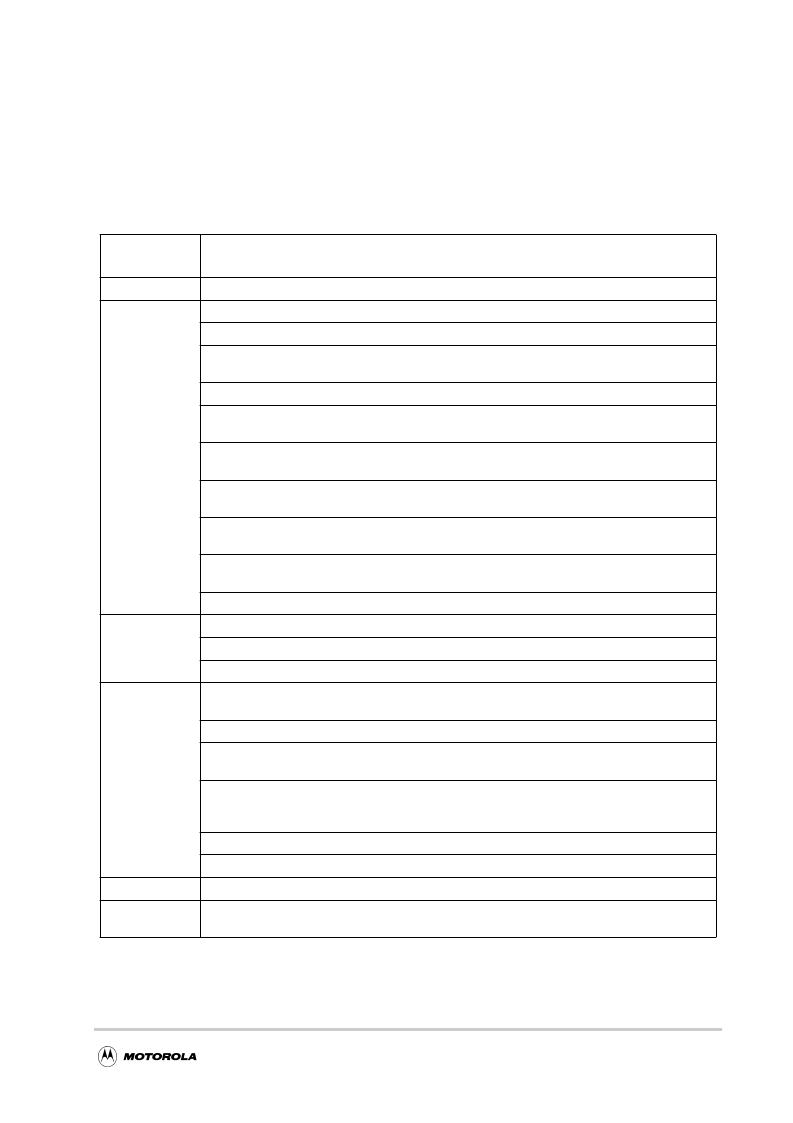

Document Revision History

1.9 Document Revision History

Table 15 lists significant changes between revisions of this document.

Table 15. Document Revision History

Document

Revision

Substantive Change(s)

Rev 0

Initial release

Rev 1

Changed VCO maximum frequency in Table 6 to 200 MHz

Changed input and Hi-Z leakage current in Table 4. from 10μA to 15μA

Changed I

and I

in Table 4 from 18mA and 14mA respectively to -7mA and 7mA to correct

the sign and reduce the current to worst case value for the lowest strength default driver

Changed footnote 4 to Table 6 to be consistent with SYSCLK jitter spec of 200ps

Modified Table 7, Figure 3, Table 8, and Figure 5 to clarify reference clock (60x Bus Clock or

SYSCLK) for input and output specifications

Changed Group I and Group II signals input setup requirement for 83 MHz in Table 7 from 3.0 ns

to 3.5 ns min.

Changed Group I-IV (non-PCI signals) input hold requirement (Spec 11a) in Table 7 from 1.0 ns

to 0 ns

Changed Group V and VI (PCI signals) input hold requirement (Spec 11b) in Table 7 from 1.0ns

to -0.5ns

Changed output valid times for all non-PCI signals (Specs 13a, 13b and 14a) from 8 ns to 7 ns at

66 Mhz and from 7 ns to 6 ns at 83 MHz

Corrected Figure 10 to reflect TOE signal is shared with DBG1 on pin U5

Rev 2

Changed input and Hi-Z leakage current, V

in

in Table 4 from 5.5V to 3.3V

Changed the power consumption data in Table 5

Changed note 7 of Table 8 to show the minimum timing specification assumes CL=0 pF

Rev 3

Deleted PLL[0-3] = 0010 from Table 11 to remove 1:1 mode operation between 16MHz and

25MHz

Added note 10 to Table 8 regarding PCI hold time

Lowered PCI 3.3V signalling output high voltage from 3.0 V to 2.7V and added current conditions

for PCI 3.3V VOH and VOL in Table 4 to reflect current production test

Included note 12 in Specification 10c of Table 4; Clarified note 9 in Table 8 and included in

Specification 12 and 18; Added a similar “guaranteed by design and not tested” note to Table 9

and included in Specifications 3, 7, and 11. All to reflect current production test.

Corrected Figure 12 dimensions from TBD to actual die size

Table 1 and Table 2 include notes on extended temperature parts.

Rev 4

Table 8, Note 8 changed to include: “These values are guaranteed by design and are not tested.”

Rev 5

Added PNS references below Table 1 and Table 6. Changed footnote ordering in Table 8,

Table 9, and Table 10. Added new footnote 2 to Table 6. Changed part number key.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC106ARX83TE | PCI Bridge/Memory Controller |

| MPC106ARX83TG | PCI Bridge/Memory Controller |

| MPC2003SG50 | 256KB and 512KB BurstRAM Secondary Cache Module for PowerPC - Based Systems |

| MPC2002SG50 | 256KB and 512KB BurstRAM Secondary Cache Module for PowerPC - Based Systems |

| MPC2002SG60 | 256KB and 512KB BurstRAM Secondary Cache Module for PowerPC - Based Systems |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC106ARX83TE | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:PCI Bridge/Memory Controller |

| MPC106ARX83TG | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:PCI Bridge/Memory Controller |

| MPC-108 | 制造商:Greenlee Textron Inc 功能描述:Unspecified Tools & Accessories ADAPTER,MATING BULKHEAD |

| MPC108100J | 功能描述:厚膜電阻器 - 透孔 MPC10 10R 5% RoHS:否 制造商:Caddock 電阻:27 kOhms 容差:1 % 功率額定值:8 W 溫度系數(shù):50 PPM / C 系列:MS 端接類型:Axial 電壓額定值:2 kV 工作溫度范圍:- 15 C to + 275 C 尺寸:8.89 mm Dia. x 23.11 mm L 封裝:Bulk |

| MPC108101J | 制造商:TE Connectivity 功能描述:RESISTOR 10 WATT 100R 5% |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。