- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385637 > MS622424 (Mosel Vitelic, Corp.) HIGH PERFORMANCE 8K x 24 BIT CMOS COLOR MAP PDF資料下載

參數(shù)資料

| 型號: | MS622424 |

| 廠商: | Mosel Vitelic, Corp. |

| 英文描述: | HIGH PERFORMANCE 8K x 24 BIT CMOS COLOR MAP |

| 中文描述: | 高性能8K的× 24位CMOS彩色地圖 |

| 文件頁數(shù): | 8/11頁 |

| 文件大小: | 70K |

| 代理商: | MS622424 |

8-8

MS622424

MOSEL V ITELIC

MS622424 Rev. 1.0 January 1995

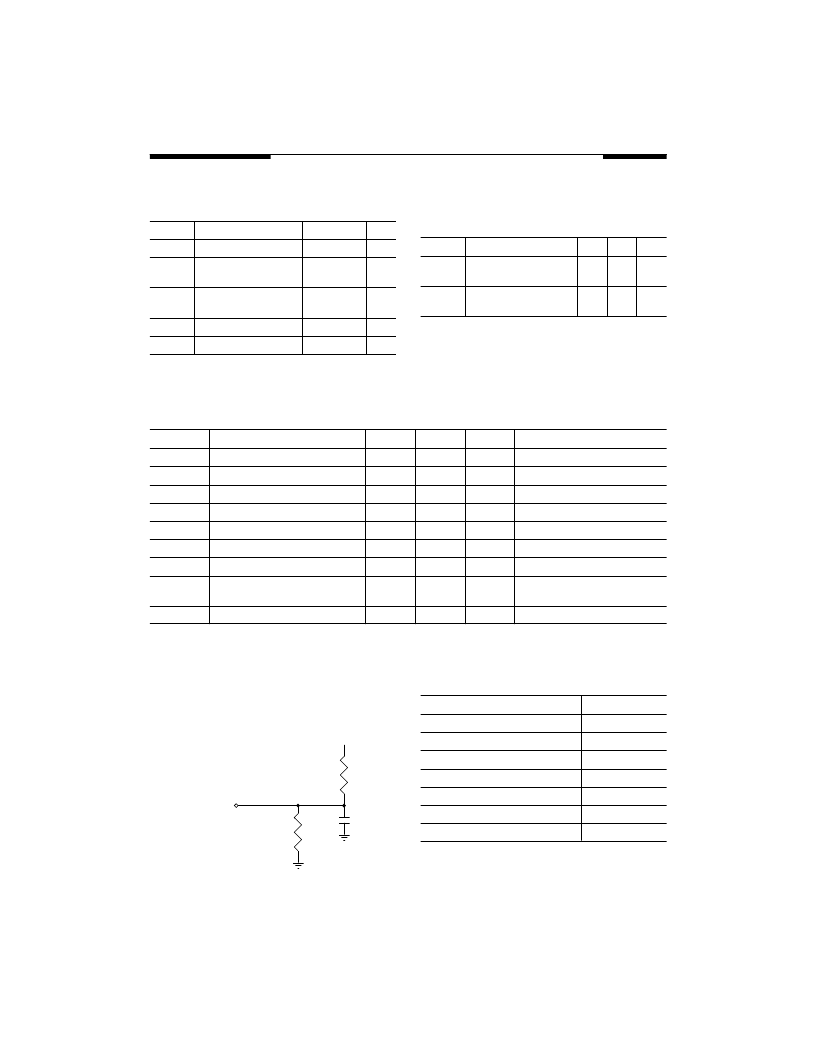

Absolute Maximum Ratings*

Symbol

Parameter

Rating

Units

V

DD

Supply Voltage

–0.5* to +7.0

V

V

T

Terminal Voltage with

Respect to V

SS

Power Dissipation

100% Duty Cycle

–0.5* to

V

DD

+0.5

TBD

V

P

D

W

t

OPR

Operating Temperature

–10 to +85

°C

t

STG

Storage Temperature

–65 to +150

°C

*Note: Operation above absolute maximum rating can affect

device reliability.

Capacitance*

T

A

= 25°C, f = 1 MHz

Symbol Parameter

Typ. Max. Unit

C

IN

Input Capacitance

(V

IN

= 0V)

5

pF

C

OUT

Output Capacitance

(V

OUT

= 0V)

8

pF

*Note: These parameters are sampled and not 100% tested.

Recommended DC and Operating Characteristics

T

A

= 0°C to 70°C, V

DD

= 5.0V ± 5%, V

SS

= 0V, unless otherwise noted. See package thermal data on pg 10.

Symbol

Parameter

Min.

Max.

Units

Test Condition

V

DD

V

SS

Supply Voltage

4.75

5.25

V

Supply Voltage

0.0

0.0

V

V

IH

Input High Voltage

2.2

V

DD

+.3

V

V

IL

I

LI

Input Low Voltage

–0.5*

+0.8

V

Input Leakage Current

–10

10

μA

V

DD

= 5.25V, V

IN

= V

SS

to V

DD

I

LO

I

DD

Output Leakage Current

–10

10

μA

V

OUT

= V

SS

to V

DD

Outputs Open, f = fmax

Dynamic Operating Current

300

mA

V

OL

Output Low Voltage

0.4

V

Active Outputs Open,

I

OL

= 4.0 mA

V

OH

Output High Voltage

2.4

V

I

OH

= –1.0 mA

* –3.5V for 20 ns pulse.

AC Test Conditions

(Applies to READ and WRITE Cycle Timing)

Input Pulse High Level

V

IH

= 3.0V

Input Pulse Low Level

V

IL

= 0.0V

Input Rise Time

t

R

= 3 ns

t

F

= 3 ns

Input Fall Time

Input and Output Reference Level

1.5V

Output Load

C

L

= 40pF, 1 TTL

V

DD

5V ± 5%

T

A

0° to +70°C

AC Test Loads

Signal transition times of 3 ns or less, timing

reference levels of 1.5V, input pulse levels of 0.0V

to 3.0V, output loading as shown in the diagram

below.

VDD

1000 Ohms

40 pF

667 Ohms

OUTPUT

Figure 2. Output Load

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MS7200L | 256 x 9, 512 x 9, 1K x 9 CMOS FIFO |

| MS7201AL | Dual-port Static RAM Based CMOS First-In/First-Out (FIFO) Memories Organized(基于雙端口靜態(tài)RAM的CMOS先進(jìn)先出存儲器) |

| MS7202AL | Dual-port Static RAM Based CMOS First-In/First-Out (FIFO) Memories Organized(基于雙端口靜態(tài)RAM的CMOS先進(jìn)先出存儲器) |

| MSA1AA001 | Coils/Delay Lines |

| MSA240 | PULSE WIDTH MODULATION AMPLIFIER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MS62256 | 制造商:MOSEL 制造商全稱:MOSEL 功能描述:32K x 8 CMOS Static RAM |

| MS62256A-25NC | 制造商:Mosel Vitelic Corporation 功能描述:Static RAM, 32Kx8, 28 Pin, Plastic, DIP |

| MS62256A-35NC | 制造商:Mosel Vitelic Corporation 功能描述:Static RAM, 32Kx8, 28 Pin, Plastic, DIP |

| MS62256A-45PC | 制造商:Mosel Vitelic Corporation 功能描述:Static RAM, 32Kx8, 28 Pin, Plastic, DIP |

| MS62256CLL-70PC | 制造商:Mosel Vitelic Corporation 功能描述:Static RAM, 32Kx8, 28 Pin, Plastic, DIP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。