- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45393 > MSM80C88A-10GS-K (OKI ELECTRIC INDUSTRY CO LTD) 8-BIT, 10 MHz, MICROPROCESSOR, PQFP56 PDF資料下載

參數(shù)資料

| 型號(hào): | MSM80C88A-10GS-K |

| 廠商: | OKI ELECTRIC INDUSTRY CO LTD |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, 10 MHz, MICROPROCESSOR, PQFP56 |

| 封裝: | 15 X 19 MM, 1 MM PITCH, PLASTIC, QFP-56 |

| 文件頁(yè)數(shù): | 17/37頁(yè) |

| 文件大小: | 267K |

| 代理商: | MSM80C88A-10GS-K |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)當(dāng)前第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)

24/37

Semiconductor

MSM80C88A-10RS/GS/JS

HALT

When a Halt instruction is executed, the CPU enters Halt state. An interrupt request or RESET

will force the MSM80C88A-10 out of the Halt state.

System Timing – Minimum Mode

A bus cycle begins at T1 with an ALE signal. The trailing edge of ALE is used to latch the address.

From T1 to T4 the IO/M signal indicates a memory or I/O operation. From T2 to T4, the address

data bus changes the address but to the data bus.

The read (RD), write (WR), and interrupt acknowledge (INTA) signals caused the addressed

device to enable the data bus. These signals become active at the beginning of T2 and inactive

at the beginning of T4.

System Timing – Maximum Mode

In maximum mode, the MSM82C88-2 Bus Controller is added to system. The CPU sends status

information to the Bus Controller. Bus timing signals are generated by the Bus Controller. Bus

timing is almost the same as in minimum mode.

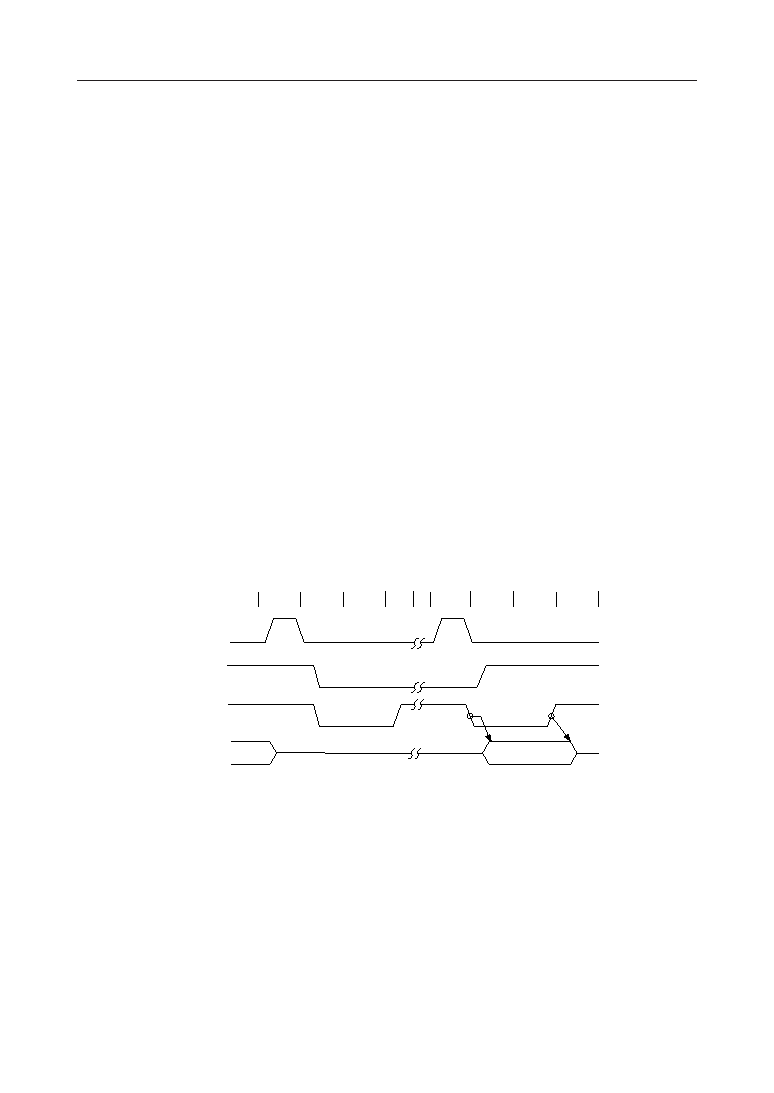

Interrupt Acknowledge Sequence

ALE

LOCK

INTA

AD0 - AD7

T1

T2

T3

T4 TI

T1

T2

T3

T4

Type Vector

Float

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSM81C55-5GS-2K | 22 I/O, PIA-GENERAL PURPOSE, PQFP44 |

| MSM82C51A-2GS-VK | 1 CHANNEL(S), 64K bps, SERIAL COMM CONTROLLER, PDSO32 |

| MSM82C51A-2JS | 1 CHANNEL(S), 64K bps, SERIAL COMM CONTROLLER, PQCC28 |

| MSM82C51A-2GS-K | 1 CHANNEL(S), 64K bps, SERIAL COMM CONTROLLER, PDSO32 |

| MSM82C53-2GS-K | 3 TIMER(S), PROGRAMMABLE TIMER, PDSO32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSM80C88A-10JS | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:8-Bit CMOS MICROPROCESSOR |

| MSM80C88A-10RS | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:8-Bit CMOS MICROPROCESSOR |

| MSM80C88A2JS | 制造商:OKI 功能描述:* |

| MSM8128 | 制造商:MOSAIC 制造商全稱:MOSAIC 功能描述:128K x 8 SRAM |

| MSM8128V-10 | 制造商:MOSAIC 制造商全稱:MOSAIC 功能描述:128K x 8 SRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。