- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄69040 > MT8952BS (ZARLINK SEMICONDUCTOR INC) 1 CHANNEL(S), 2.5M bps, SERIAL COMM CONTROLLER, PDSO28 PDF資料下載

參數(shù)資料

| 型號: | MT8952BS |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 1 CHANNEL(S), 2.5M bps, SERIAL COMM CONTROLLER, PDSO28 |

| 封裝: | 0.300 INCH, MS-013AE, SOIC-28 |

| 文件頁數(shù): | 5/32頁 |

| 文件大小: | 602K |

| 代理商: | MT8952BS |

第1頁第2頁第3頁第4頁當前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

MT8952B

Data Sheet

13

Zarlink Semiconductor Inc.

Rx15/19 FULL - Receive FIFO 15/19 full: This bit when HIGH, confirms that the receive FIFO has 15 bytes in it

and it can receive four more bytes.

Rx OFLW - Receive FIFO overflow: This bit when set HIGH, indicates that the receive FIFO is full and a ‘write’

occurred indicating an overflow. The byte causing this and all the subsequent bytes written while the FIFO is in this

state are lost. The receiver begins to search for a new start flag.

Watchdog Timer Register (Write)

The Watchdog Timer Register operates in conjunction with the Watchdog Timer and the WD output. Writing the

code of XXX0 1010 in the register resets the WD timer. If the register is not re-written within 210 cycles of F0i after

resetting the timer, the WD output goes LOW. This register serves the sole purpose of resetting the timer and hence

relevant only if it is written with the above data.

Interrupt Enable Register (Read/Write)

This register enables/disables the interrupts as specified in the Interrupt Flag Register (IFR). Setting HIGH the

appropriate bits in this register (IER) enables the associated interrupt source. However, the masked bits in the IFR

are still valid but they do not cause the IRQ output to go LOW. The description of the bits enabling the various

interrupts is identical to those of the Interrupt Flag Register.

General Status Register (Read)

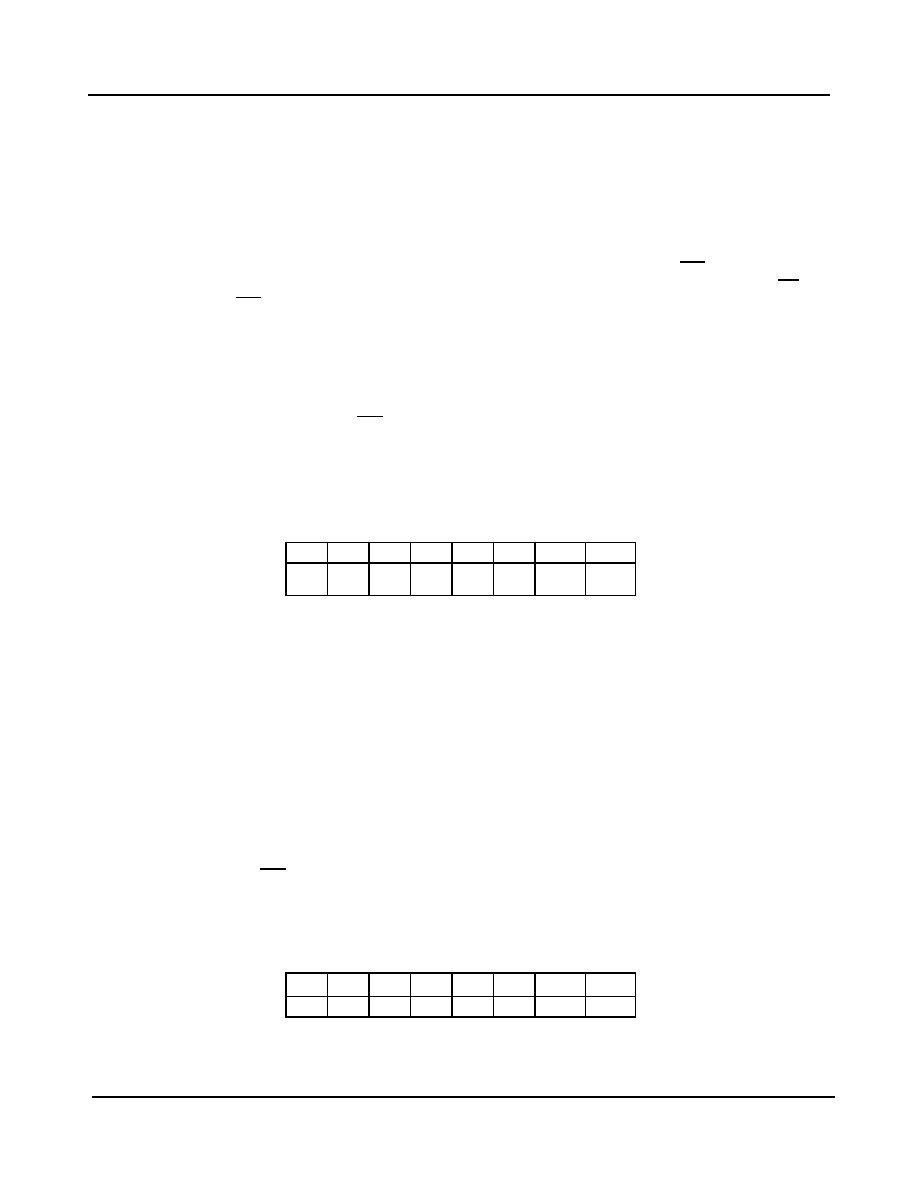

This register (Figure 12) contains the general status information on the Protocol Controller.

Figure 12 - General Status Register

Rx OFLW - Receive FIFO overflow: This bit, if set HIGH, indicates that the receive FIFO has overflowed. The byte

causing this and all the subsequent bytes written while the FIFO is in this state are lost. Note that this bit is the

same as the Rx OFLW bit in Interrupt Flag Register (IFR) and can only be cleared by reading the IFR.

Tx URUN - Transmit FIFO Underrun: When HIGH, this bit indicates that the transmit FIFO has underrun. Under

this condition the packet being transmitted is aborted. This bit is the same as the Tx URUN bit in the Interrupt Flag

Register (IFR) and can only be cleared when the IFR is read.

GA - Go Ahead: This bit is set HIGH if a ‘go ahead’ is received on the incoming data stream and is cleared when

the Interrupt Flag Register is read. This bit is the same as the GA bit in the IFR.

ABRT - Abort: The reception of contiguous seven ONEs on incoming data, sets this bit HIGH and reading the

General Status Register, clears it.

IRQ - Interrupt Request: This bit refers to the status of the interrupt request output from the Protocol Controller. If

HIGH, it indicates that the IRQ (pin 6) output is LOW and vice versa.

IDLE - Idle Channel: This bit, if set HIGH, identifies that the receiver is detecting an idle channel at its input

(minimum 15 ONEs).

C-Channel Status Register (Read)

Figure 13 - C-Channel Status Register

D7

D6

D5

D4

D3

D2

D1

D0

Rx

OFLW

Tx

URUN

GA

ABRT

IRQ

IDLE

LOW

HIGH

D7

D6

D5

D4

D3

D2

D1

D0

CR7

CR6

CR5

CR4

CR3

CR2

CR1

CR0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT8952BPR | 1 CHANNEL(S), 2.5M bps, SERIAL COMM CONTROLLER, PQCC28 |

| MT8952BP1 | 1 CHANNEL(S), 2.5M bps, SERIAL COMM CONTROLLER, PQCC28 |

| MTA41110/P | SPECIALTY MICROPROCESSOR CIRCUIT, PDIP18 |

| MTA41110/SO | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO18 |

| MTR80C186-12 | 16-BIT, 12.5 MHz, MICROPROCESSOR, CQCC68 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT8952BS1 | 制造商:Microsemi Corporation 功能描述:PB FREE HDLC PROTOCOL CONTROLLER - Rail/Tube 制造商:Zarlink Semiconductor Inc 功能描述:PB FREE HDLC PROTOCOL CONTROLLER |

| MT8960 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Integrated PCM Filter Codec |

| MT8960AE | 制造商:ZARLINK 功能描述: |

| MT8960AE1 | 制造商:Microsemi Corporation 功能描述:AUD CODEC 1ADC / 1DAC 18PDIP - Rail/Tube |

| MT8961 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:ISO2-CMOS Integrated PCM Filter Codec |

發(fā)布緊急采購,3分鐘左右您將得到回復。