- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄383724 > ORT82G5 ORCA ORT82G5 1.0.1-25/2.0-2.5/3.125 Gbits/s Backplane Interface FPSC PDF資料下載

參數(shù)資料

| 型號(hào): | ORT82G5 |

| 英文描述: | ORCA ORT82G5 1.0.1-25/2.0-2.5/3.125 Gbits/s Backplane Interface FPSC |

| 中文描述: | ORCA的ORT82G5 1.0.1-25/2.0-2.5/3.125 Gb /秒背板接口促進(jìn)文化基金 |

| 文件頁(yè)數(shù): | 36/92頁(yè) |

| 文件大?。?/td> | 1823K |

| 代理商: | ORT82G5 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)當(dāng)前第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)

36

Agere Systems Inc.

Preliminary Data Sheet

July 2001

1.0-1.25/2.0-2.5/3.125 Gbits/s Backplane Interface

ORCA

ORT82G5 FPSC Eight-Channel

Memory Map

Definition of Register Types

The registers in ORT82G5 are 8-bit memory locations, which in general can be classified into the following types:

Status Register and Control Register.

Status Register

Read-only register to convey the status information of various operations within the FPSC core. An example is the

state of the XAUI link-state-machine.

Control Register

Read-write register to set up the control inputs that define the operation of the FPSC core.

The SERDES block within the ORT82G5 core has a set of status and control registers for it

’

s operation. The

detailed description of them can be found in the SERDES data sheet.

There is another group of status and control registers which are implemented outside the SERDES, which are

related to the SERDES and other functional blocks in the FPSC core. They will be described in detail here. Each

SERDES has four independent channels, which are named A, B, C, or D. Using this nomenclature, the SERDES A

channels are named as AA, AB, AC, and AD, while SERDES B channels will be BA, BB, BC, and BD.

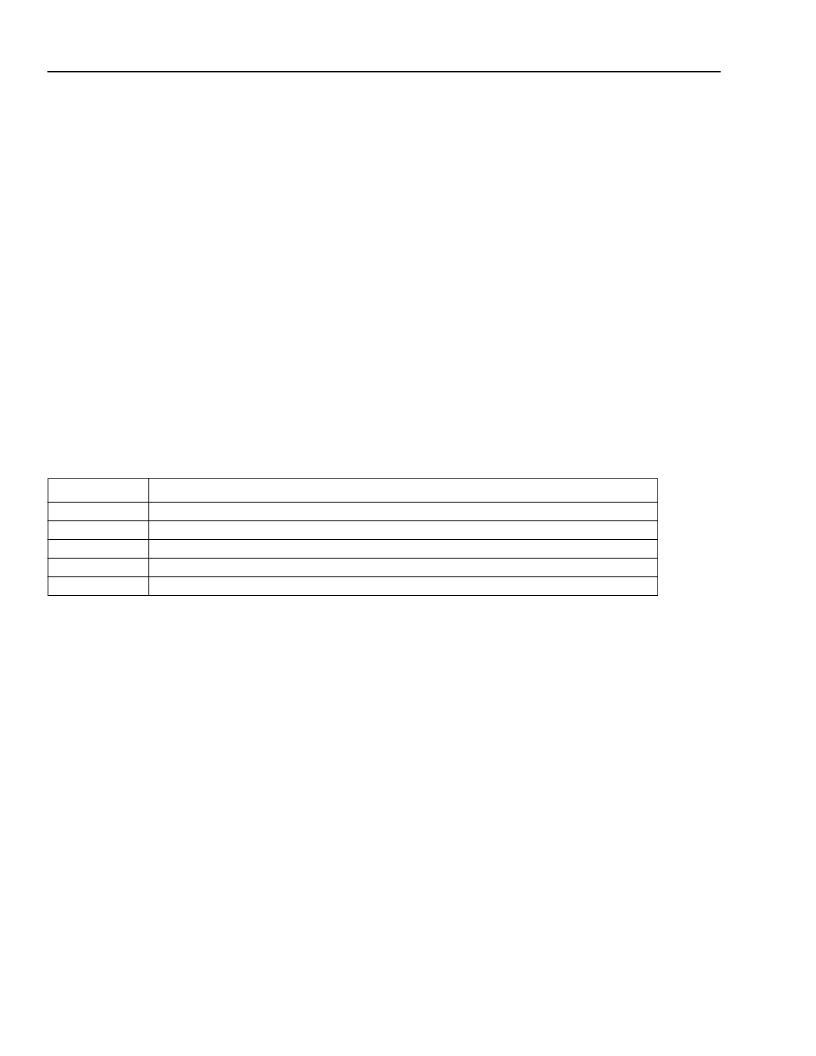

Table 11. Structural Register Elements

A full memory map is included in Table 12.

Address (Hex)

300xx

301xx

308xx

309xx

30A0x

Description

SERDES A, internal registers.

SERDES B, internal registers.

Channel A [A:D] registers (external to SERDES blocks).

Channel B [A:D] registers (external to SERDES blocks).

Global registers (external to SERDES blocks).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ORT8850 | Field-Programmable System Chip (FPSC) Eight-Channel x 850 Mbits/s Backplane Transceiver |

| ORT8850H | Field-Programmable System Chip (FPSC) Eight-Channel x 850 Mbits/s Backplane Transceiver |

| ORT8850L | Field-Programmable System Chip (FPSC) Eight-Channel x 850 Mbits/s Backplane Transceiver |

| OS1001 | Interface IC |

| OS1010 | Optoelectronic |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ORT82G5-1BM680C | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 10368 LUT 372 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| ORT82G5-1BM680I | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 10368 LUT 372 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| ORT82G5-1F680C | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 ORCA FPSC 3.7GBITS/s BP XCVR 643K RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| ORT82G5-1F680I | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 ORCA FPSC 2.7Gbits/s BP XCVR 643K RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| ORT82G5-1FN680C | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 ORCA FPSC 1.5V 3.7 G b Bpln Xcvr 643K Gt RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。