- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369944 > P82C55A (INTEL CORP) CHMOS PROGRAMMABLE PERIPHERAL INTERFACE PDF資料下載

參數(shù)資料

| 型號: | P82C55A |

| 廠商: | INTEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | CHMOS PROGRAMMABLE PERIPHERAL INTERFACE |

| 中文描述: | 24 I/O, PIA-GENERAL PURPOSE, PDIP40 |

| 封裝: | DIP-40 |

| 文件頁數(shù): | 5/23頁 |

| 文件大?。?/td> | 325K |

| 代理商: | P82C55A |

82C55A

82C55A OPERATIONAL DESCRIPTION

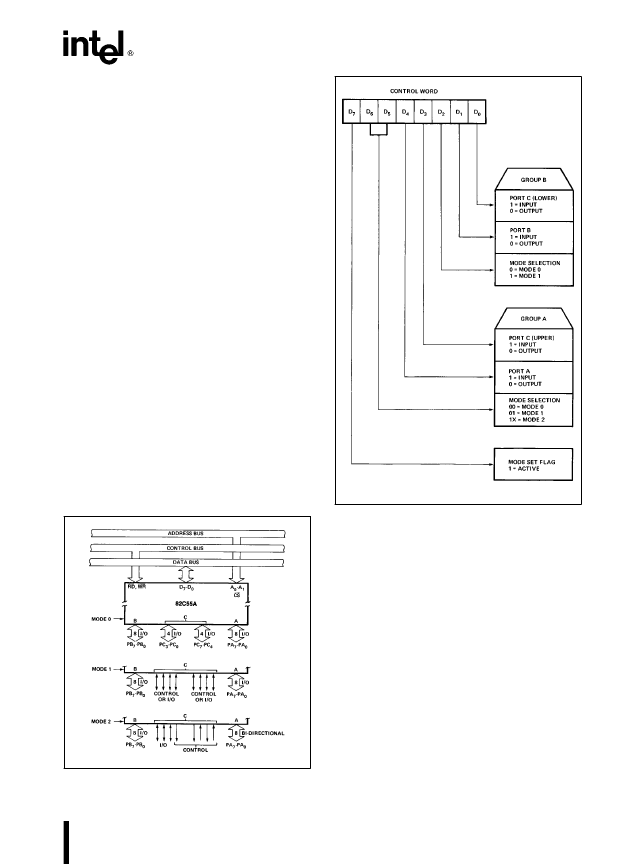

Mode Selection

There are three basic modes of operation that can

be selected by the system software:

Mode 0 D Basic input/output

Mode 1 D Strobed Input/output

Mode 2 D Bi-directional Bus

When the reset input goes ‘‘high’’ all ports will be set

to the input mode with all 24 port lines held at a logic

‘‘one’’ level by the internal bus hold devices (see

Figure 4 Note). After the reset is removed the

82C55A can remain in the input mode with no addi-

tional initialization required. This eliminates the need

for pullup or pulldown devices in ‘‘a(chǎn)ll CMOS’’ de-

signs. During the execution of the system program,

any of the other modes may be selected by using a

single output instruction. This allows a single

82C55A to service a variety of peripheral devices

with a simple software maintenance routine.

The modes for Port A and Port B can be separately

defined, while Port C is divided into two portions as

required by the Port A and Port B definitions. All of

the output registers, including the status flip-flops,

will be reset whenever the mode is changed. Modes

may be combined so that their functional definition

can be ‘‘tailored’’ to almost any I/O structure. For

instance; Group B can be programmed in Mode 0 to

monitor simple switch closings or display computa-

tional results, Group A could be programmed in

Mode 1 to monitor a keyboard or tape reader on an

interrupt-driven basis.

231256–5

Figure 5. Basic Mode Definitions and Bus

Interface

231256–6

Figure 6. Mode Definition Format

The mode definitions and possible mode combina-

tions may seem confusing at first but after a cursory

review of the complete device operation a simple,

logical I/O approach will surface. The design of the

82C55A has taken into account things such as effi-

cient PC board layout, control signal definition vs PC

layout and complete functional flexibility to support

almost any peripheral device with no external logic.

Such design represents the maximum use of the

available pins.

Single Bit Set/Reset Feature

Any of the eight bits of Port C can be Set or Reset

using a single OUTput instruction. This feature re-

duces software requirements in Control-based appli-

cations.

When Port C is being used as status/control for Port

A or B, these bits can be set or reset by using the Bit

Set/Reset operation just as if they were data output

ports.

5

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P8344AH | HIGH PERFORMANCE 8 BIT MICROCONTROLLER WITH ON CHIP SERIAL COMMUNICATION CONTROLLER |

| P8044AH | HIGH PERFORMANCE 8 BIT MICROCONTROLLER WITH ON CHIP SERIAL COMMUNICATION CONTROLLER |

| P8744AH | HIGH PERFORMANCE 8 BIT MICROCONTROLLER WITH ON CHIP SERIAL COMMUNICATION CONTROLLER |

| P83C524EFA | CONN, JACK MODULAR 90DEG 4P 4C |

| P83C524EFP | CONN HEADER 12POS SGL PCB 30GOLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P82C55A2 | 制造商:Intel 功能描述: |

| P82C55A-2 | 制造商:Rochester Electronics LLC 功能描述: |

| P82C574 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral Interface |

| P82C59A2 | 制造商:INTEL 功能描述:* 制造商:Intel 功能描述: |

| P82C59A-2 | 制造商:Intel 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。