- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367800 > PC755CVGSU366LE (ATMEL CORP) PowerPC 755/745 RISC Microprocessor PDF資料下載

參數(shù)資料

| 型號(hào): | PC755CVGSU366LE |

| 廠商: | ATMEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | PowerPC 755/745 RISC Microprocessor |

| 中文描述: | 32-BIT, 366 MHz, RISC PROCESSOR, CBGA360 |

| 封裝: | SOLDER COLUMN INTERPOSER, CERAMIC, BGA-360 |

| 文件頁(yè)數(shù): | 27/50頁(yè) |

| 文件大?。?/td> | 1064K |

| 代理商: | PC755CVGSU366LE |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)當(dāng)前第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)

27

PC755/745

2138D–HIREL–06/03

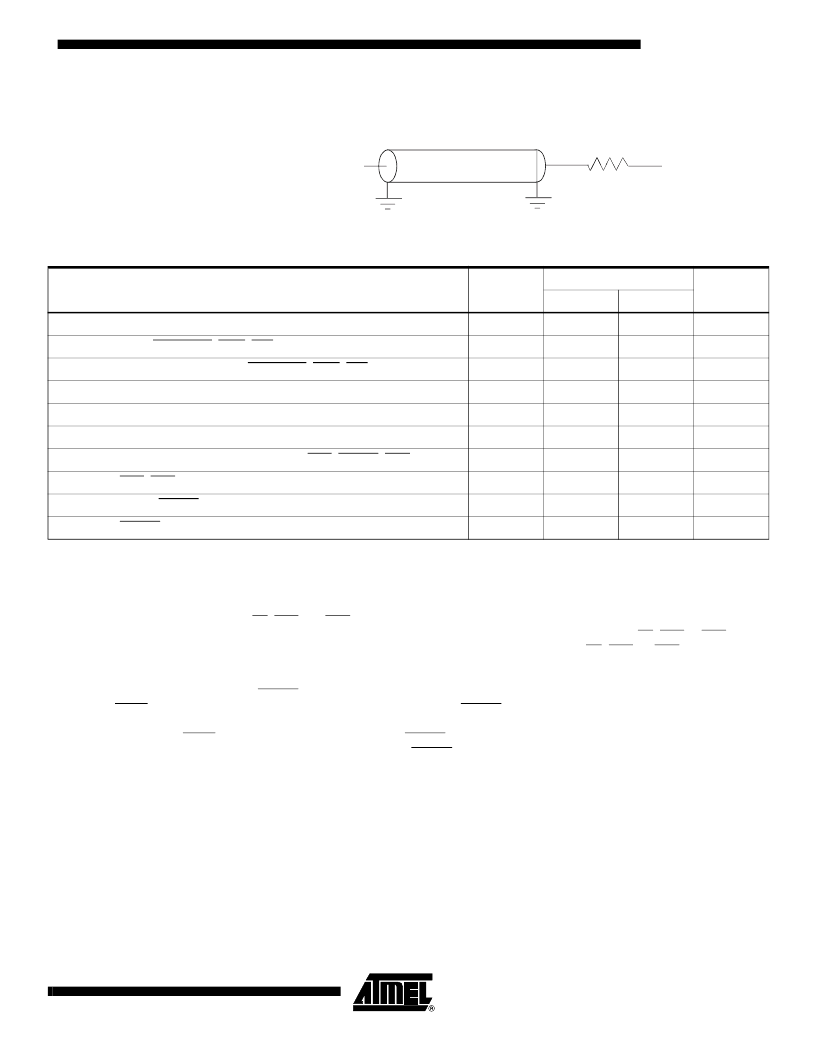

Figure 12 provides the AC test load for the PC755.

Figure 12.

AC Test Load

Notes:

1. Revisions prior to Rev 2.8 (Rev E) were limited in performance and did not conform to this specification. Contact your local

Motorola sales office for more information.

2. Guaranteed by design and characterization.

3. t

SYSCLK

is the period of the external clock (SYSCLK) in nanoseconds (ns). The numbers given in the table must be multiplied

by the period of SYSCLK to compute the actual time duration (in ns) of the parameter in question.

4. Per the 60x bus protocol, TS, ABB and DBB are driven only by the currently active bus master. They are asserted low then

precharged high before returning to high-Z as shown in Figure 6. The nominal precharge width for TS, ABB or DBB is 0.5 x

t

, i.e. less than the minimum t

period, to ensure that another master asserting TS, ABB, or DBB on the following

clock will not contend with the precharge. Output valid and output hold timing is tested for the signal asserted. Output valid

time is tested for precharge.The high-Z behavior is guaranteed by design.

5. Per the 60x bus protocol, ARTRY can be driven by multiple bus masters through the clock period immediately following

AACK. Bus contention is not an issue since any master asserting ARTRY will be driving it low. Any master asserting it low in

the first clock following AACK will then go to high-Z for one clock before precharging it high during the second cycle after the

assertion of AACK. The nominal precharge width for ARTRY is 1.0 t

; i.e., it should be high-Z as shown in Figure 6

before the first opportunity for another master to assert ARTRY. Output valid and output hold timing is tested for the signal

asserted. Output valid time is tested for precharge. The high-Z and precharge behavior is guaranteed by design.

OVDD/2

OUTPUT

Z0 = 50

R

L

= 50

Table 14.

Processor Bus AC Timing Specifications

(1)

at Recommended Operating Conditions

Parameter

Symbols

All Speed Grades

Unit

Min

Max

Setup Times: All Inputs

t

IVKH

2.5

–

ns

Input Hold Times:

TLBISYNC

,

MCP

,

SMI

t

IXKH

0.6

–

ns

Input Hold Times: All Inputs, except

TLBISYNC

,

MCP

,

SMI

t

IXKH

0.2

–

ns

Valid Times: All Outputs

t

KHOV

–

4.1

ns

Output Hold Times: All Outputs

t

KHOX

1

–

ns

SYSCLK to Output Enable

(2)

t

KHOE

0.5

–

ns

SYSCLK to Output High Impedance (all except

ABB

,

ARTRY

,

DBB

)

(2)

t

KHOZ

–

6

ns

SYSCLK to

ABB

,

DBB

High Impedance After Precharge

(2)(3)(4)

t

KHABPZ

–

1

t

SYSCLK

Maximum Delay to

ARTRY

Precharge

(2)(3)(5)

t

KHARP

–

1

t

SYSCLK

SYSCLK to

ARTRY

High Impedance After Precharge

(2)(3)(5)

t

KHARPZ

–

2

t

SYSCLK

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PC755CVGSU400LE | PowerPC 755/745 RISC Microprocessor |

| PC812B | NPN-OUTPUT DC-INPUT OPTOCOUPLER |

| PC812A | |

| PC812C | NPN-OUTPUT DC-INPUT OPTOCOUPLER |

| PC812 | High Noise Resistance Type Photocoupler |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PC755CVGSU400LE | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:PowerPC 755/745 RISC Microprocessor |

| PC755CVGU300LE | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:PowerPC 755/745 RISC Microprocessor |

| PC755CVGU350LE | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:PowerPC 755/745 RISC Microprocessor |

| PC755CVGU366LE | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:PowerPC 755/745 RISC Microprocessor |

| PC755CVGU400LE | 制造商:e2v technologies 功能描述:MPU RISC 32BIT 0.22UM 400MHZ 2.5V/3.3V 360CBGA - Trays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。