- 您現在的位置:買賣IC網 > PDF目錄370007 > PLS159AN (NXP SEMICONDUCTORS) Programmable logic sequencer 16 】 45 】 12 PDF資料下載

參數資料

| 型號: | PLS159AN |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | PLD |

| 英文描述: | Programmable logic sequencer 16 】 45 】 12 |

| 中文描述: | OT PLD, 35 ns, PDIP20 |

| 封裝: | 0.300 INCH, PLASTIC, DIP-20 |

| 文件頁數: | 9/12頁 |

| 文件大小: | 132K |

| 代理商: | PLS159AN |

Philips Semiconductors Programmable Logic Devices

Product specification

PLS159A

Programmable logic sequencer

(16

×

45

×

12)

October 22, 1993

33

LOGIC PROGRAMMING

The PLS159A is fully supported by industry

standard (JEDEC compatible) PLD CAD

tools, including Philips Semiconductors’

SNAP, Data I/O Corporation’s ABEL

and

Logical Devices Inc.’s CUPL

design

software packages.

All packages allow Boolean and state

equation entry formats. SNAP, ABEL and

CUPL also accept, as input, schematic

capture format.

PLS159A logic designs can also be

generated using the program table entry

format detailed on the following pages. This

program table entry format is supported by

the Philips Semiconductors SNAP PLD

design software package.

To implement the desired logic functions, the

state of each logic variable from logic

equations (I, B, O, P, etc.) is assigned a

symbol. The symbols for TRUE,

COMPLEMENT, INACTIVE, PRESET, etc.,

are defined below.

PROGRAMMING AND

SOFTWARE SUPPORT

Refer to Section 9

(Development Software)

and Section 10

(Third-party Programmer/

Software Support)

of this data handbook for

additional information.

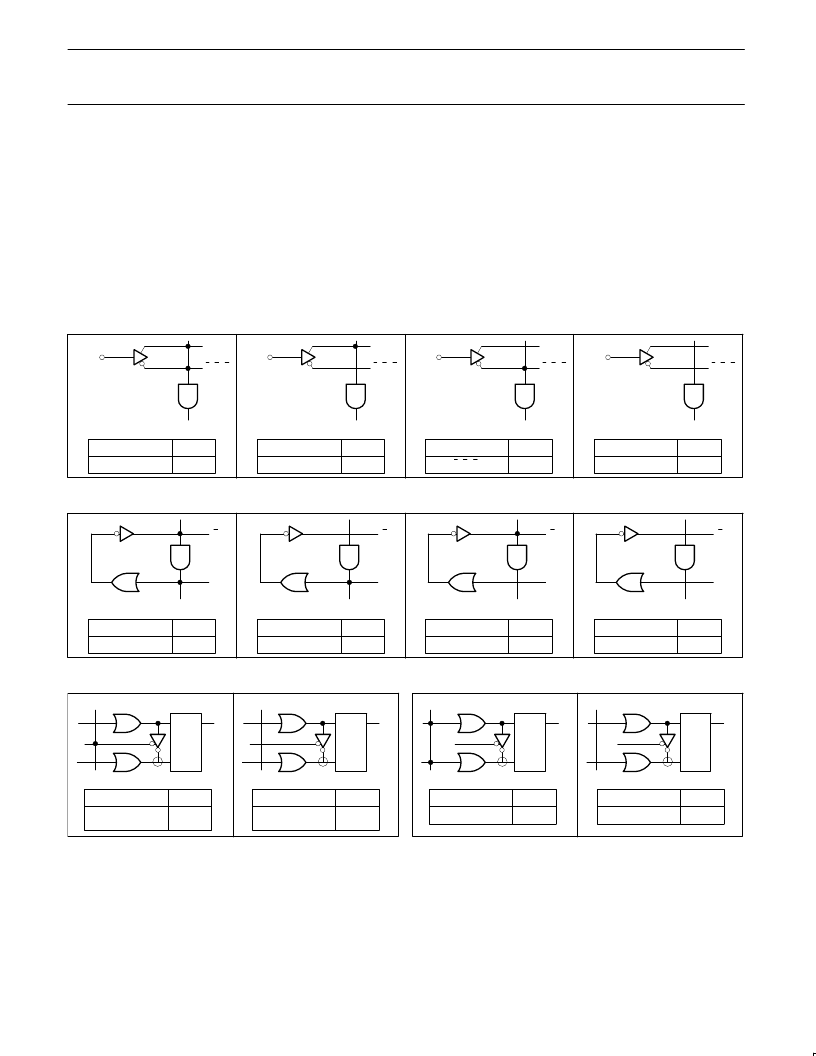

“AND” ARRAY – (I), (B), (Qp)

STATE

DON’T CARE

CODE

STATE

I, B, Q

CODE

L

STATE

I, B, Q

CODE

STATE

INACTIVE

1, 2

CODE

O

–

H

(T, F

C

, L, P, R, D)

n

I, B, Q

I, B, Q

I, B, Q

(T, F

C

, L, P, R, D)

n

I, B, Q

I, B, Q

I, B, Q

(T, F

C

, L, P, R, D)

n

I, B, Q

I, B, Q

I, B, Q

(T, F

C

, L, P, R, D)

n

I, B, Q

I, B, Q

I, B, Q

“COMPLEMENT” ARRAY – (C)

ACTION

TRANSPARENT

CODE

ACTION

PROPAGATE

CODE

ACTION

GENERATE

5

CODE

ACTION

INACTIVE

1, 3, 5

CODE

O

–

A

C

C

(T

n

, F

C

)

C

C

(T

n

, F

C

)

C

C

(T

n

, F

C

)

C

C

(T

n

, F

C

)

“OR” ARRAY – (F-F CONTROL MODE)

“OR” ARRAY – (Q

n

= D-Type)

Q

J

K

Q

J

K

F

C

ACTION

J–K OR D

(CONTROLLED)

1

CODE

A

F

C

M

M

ACTION

J–K ONLY

CODE

Q

J

K

Q

J

K

T

n

T

n

STATUS

ACTIVE (Set)

1

CODE

A

T

n

M = ENABLED

INACTIVE (Reset)

CODE

M = ENABLED

T

n

STATUS

ENABLED

DISABLED

CAUTION:

THE PLS159A Programming Algorithm is different from the PLS159.

Notes on following page.

相關PDF資料 |

PDF描述 |

|---|---|

| PLS173A | Programmable logic array 22 】 42 】 10 |

| PLS173N | Programmable logic array 22 】 42 】 10 |

| PLS179A | Fuse-Programmable PLD |

| PLS179N | High Speed, 16-Bit, 500ksps Sampling A/D Converter with Shutdown; Package: SSOP; No of Pins: 36; Temperature Range: 0°C to +70°C |

| PLS30S16-40JC | 16-Bit, 200ksps, Serial Sampling ADC; Package: SSOP; No of Pins: 28; Temperature Range: 0°C to +70°C |

相關代理商/技術參數 |

參數描述 |

|---|---|

| PLS159AN-B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Fuse-Programmable PLD |

| PLS167/BLA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Fuse-Programmable PLD |

| PLS167-33 | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:24-PIN TTL/CMOS PROGRAMMABLE LOGIC SEQUENCERS |

| PLS167-33CFN | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:24-PIN TTL/CMOS PROGRAMMABLE LOGIC SEQUENCERS |

| PLS167-33CJS | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:24-PIN TTL/CMOS PROGRAMMABLE LOGIC SEQUENCERS |

發(fā)布緊急采購,3分鐘左右您將得到回復。