- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361292 > QL5064-33APB456I BUS CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | QL5064-33APB456I |

| 英文描述: | BUS CONTROLLER |

| 中文描述: | 總線控制器 |

| 文件頁數(shù): | 21/37頁 |

| 文件大小: | 806K |

| 代理商: | QL5064-33APB456I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

QL5064 QuickPCI Data Sheet Rev D

21

QL5064 QuickPCI Data Sheet

20.0 AC Characteristics at Vcc = 3.3V, TA=25° C (K=1.00)

The AC Specifications, Logic Cell diagrams and waveforms are provided below. To calculate delays,

multiply the appropriate K factor in the “Operating Range” section by the following numbers.

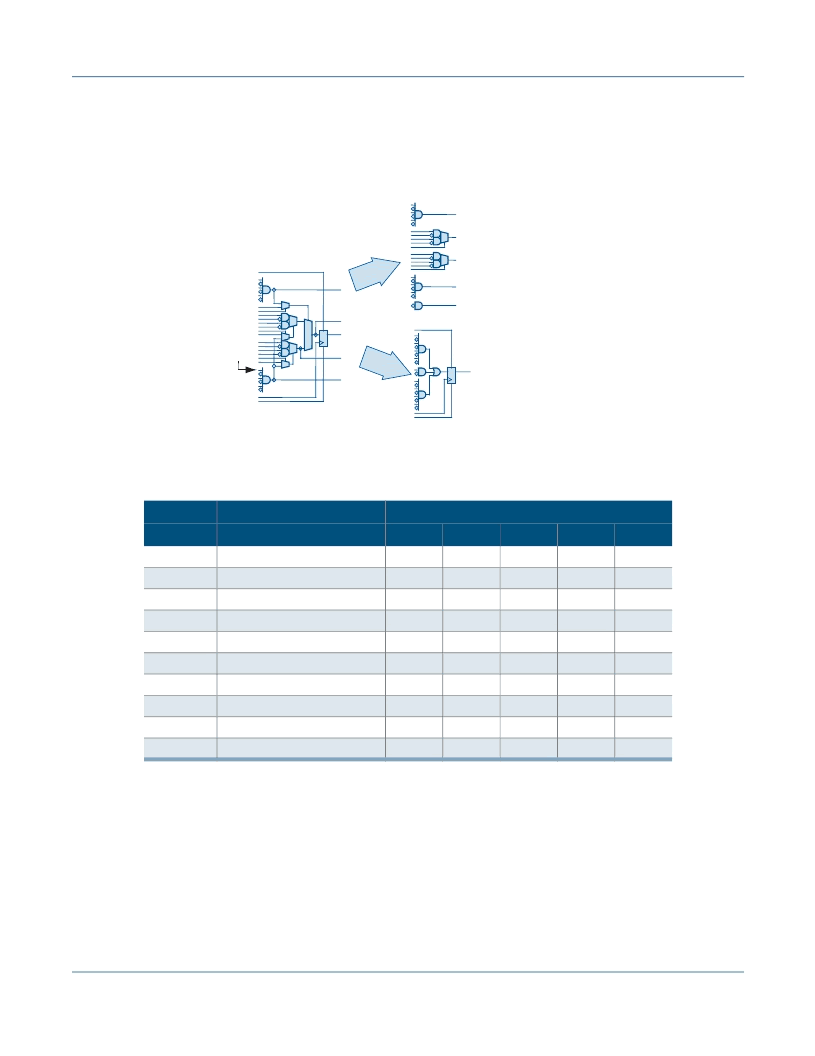

Figure 12: QuickPCI Logic Cell Configuration

Table 2: Logic Cells

Symbol

Parameter

Propagation Delays (ns)Fanout a

a. Stated timing for worst case Propagation Delay over process variation at VCC=3.3V and TA=25×C.

Multiply by the appropriate Delay Factor, K, for speed grade, voltage and temperature settings as

specified in the Operating Range.

b. These limits are derived from a representative selection of the slowest paths through the Quick-

RAM logic cell including typical net delays. Worst case delay values for specific paths should be

determined from timing analysis of your particular design.

1

2

3

4

8

tPD

Combinatorial Delay b

1.4

1.7

2.0

2.3

3.5

tSU

Setup Time

b

1.8

1.8

1.8

1.8

1.8

tH

Hold Time

0.0

0.0

0.0

0.0

0.0

tCLK

Clock to Q Delay

0.8

1.1

1.4

1.7

2.9

tCWHI

Clock High Time

1.6

1.6

1.6

1.6

1.6

tCWLO

Clock Low Time

1.6

1.6

1.6

1.6

1.6

tSET

Set Delay

1.4

1.7

2.0

2.3

3.5

tRESET

Reset Delay

1.2

1.5

1.8

2.1

3.3

tSW

Set Width

1.9

1.9

1.9

1.9

1.9

tRW

Reset Width

1.8

1.8

1.8

1.8

1.8

Programmable

Logic Cell

5 Independent

Functions

(Optimized

for Synthesis)

OR

Single Large

Function

F1

相關PDF資料 |

PDF描述 |

|---|---|

| QL5064-33APB484C | BUS CONTROLLER |

| QL5064-33APB484I | BUS CONTROLLER |

| QL5064-33BPB456C | BUS CONTROLLER |

| QL5064-33BPB456I | BUS CONTROLLER |

| QL5064-33BPB484C | BUS CONTROLLER |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| QL5064-66APS484C-5541 | 制造商:QuickLogic Corporation 功能描述: |

| QL5064-66APS484I-5541 | 制造商:QuickLogic Corporation 功能描述: |

| QL5064-66BPS484C-5725 | 制造商:QuickLogic Corporation 功能描述: |

| QL5064-75CPS484C-5616 | 制造商:QuickLogic Corporation 功能描述: |

| QL5064-75CPS484I-5612 | 制造商:QuickLogic Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。