- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361292 > QL5064-33APB456I BUS CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | QL5064-33APB456I |

| 英文描述: | BUS CONTROLLER |

| 中文描述: | 總線控制器 |

| 文件頁數(shù): | 23/37頁 |

| 文件大小: | 806K |

| 代理商: | QL5064-33APB456I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

QL5064 QuickPCI Data Sheet Rev D

23

QL5064 QuickPCI Data Sheet

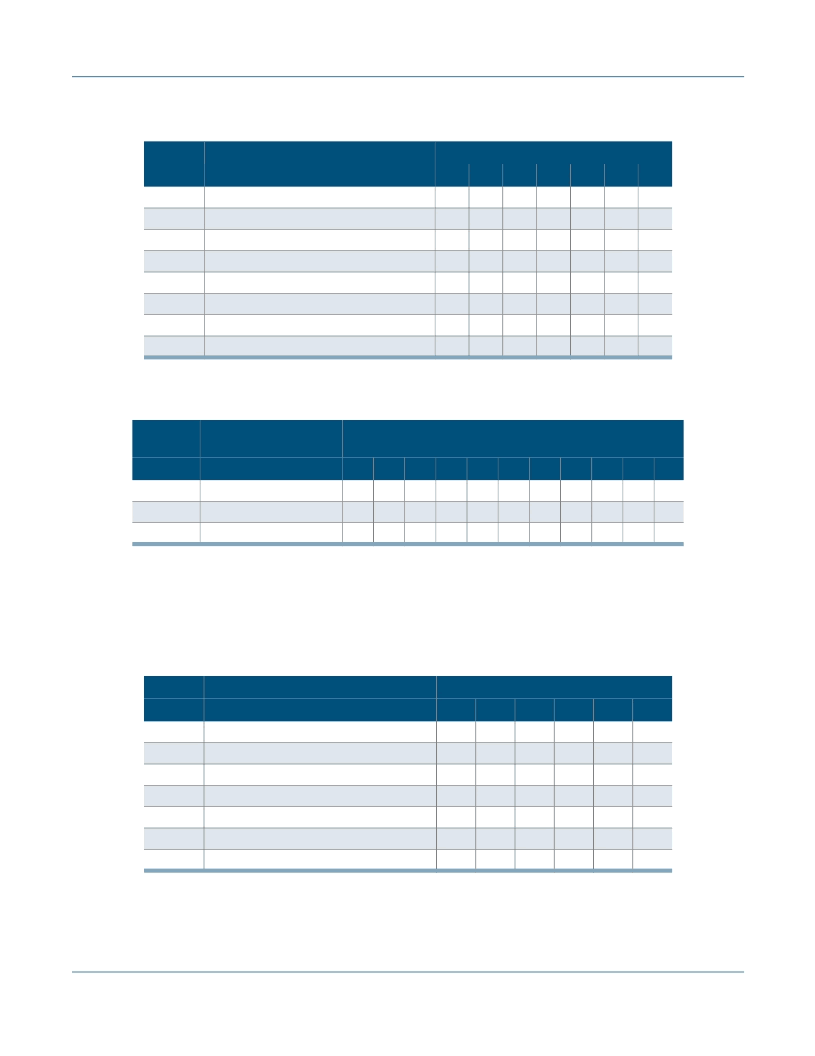

Table 6: Input-Only Cells

Symbol

Parameter

Propagation Delays (ns)Fanout

b

1

2

3

4

8

12

24

TIN

High Drive Input Delay

1.5

1.6

1.8

1.9

2.4

2.9

4.4

TINI

High Drive Input, Inverting Delay

1.6

1.7

1.9

2.0

2.5

3.0

4.5

TISU

Input Register Set-Up Time

3.1

3.1

3.1

3.1

3.1

3.1

3.1

TIH

Input Register Hold Time

0.0

0.0

0.0

0.0

0.0

0.0

0.0

TlCLK

Input Register Clock To Q

0.7

0.8

1.0

1.1

1.6

2.1

3.6

TlRST

Input Register Reset Delay

0.6

0.7

0.9

1.0

1.5

2.0

3.5

TlESU

Input Register Clock Enable Setup Time

2.3

2.3

2.3

2.3

2.3

2.3

2.3

TlEH

Input Register Clock Enable Hold Time

0.0

0.0

0.0

0.0

0.0

0.0

0.0

Table 7: Clock Cells

Symbols

Parameter

Propagation Delays (ns)

Loads per Half Column [a]

a. The array distributed networks consist of 40 half columns and the global distributed networks consist

of 44 half columns, each driven by an independent buffer. The number of half columns used does not

affect clock buffer delay. The array clock has up to 8 loads per half column. The global clock has up

to 11 loads per half column.

1

2

3

4

8

10

12

14

16

18

20

tACK

Array Clock Delay

1.2

1.2

1.3

1.3

1.5

.16

1.7

1.8

1.9

2

2.1

tGCKP

Global Clock Pin Delay

0.7

0.7

0.7

0.7

0.7

0.7

0.7

0.7

0.7

0.7

0.7

tGCKB

Global Clock Buffer Delay

0.8

0.8

0.9

0.9

1.1

1.2

1.3

1.4

1.5

1.6

1.7

Table 8: I/O Cell Input Delays

Symbol

Parameter

Propagation Delays (ns)Fanout [4]

1

2

3

4

8

10

tI/O

Input Delay (bidirectional pad)

1.3

1.6

1.8

2.1

3.1

3.6

TISU

Input Register Set-Up Time

3.1

3.1

3.1

3.1

3.1

3.1

TIH

Input Register Hold Time

0.0

0.0

0.0

0.0

0.0

0.0

TlOCLK

Input Register Clock To Q

0.7

1.0

1.2

1.5

2.5

3.0

TlORST

Input Register Reset Delay

0.6

0.9

1.1

1.4

2.4

2.9

TlESU

Input Register clock Enable Set-Up Time

2.3

2.3

2.3

2.3

2.3

2.3

TlEH

Input Register Clock Enable Hold Time

0.0

0.0

0.0

0.0

0.0

0.0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| QL5064-33APB484C | BUS CONTROLLER |

| QL5064-33APB484I | BUS CONTROLLER |

| QL5064-33BPB456C | BUS CONTROLLER |

| QL5064-33BPB456I | BUS CONTROLLER |

| QL5064-33BPB484C | BUS CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| QL5064-66APS484C-5541 | 制造商:QuickLogic Corporation 功能描述: |

| QL5064-66APS484I-5541 | 制造商:QuickLogic Corporation 功能描述: |

| QL5064-66BPS484C-5725 | 制造商:QuickLogic Corporation 功能描述: |

| QL5064-75CPS484C-5616 | 制造商:QuickLogic Corporation 功能描述: |

| QL5064-75CPS484I-5612 | 制造商:QuickLogic Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。