- 您現(xiàn)在的位置:買賣IC網 > PDF目錄373273 > RH80532NC025256 Microprocessor PDF資料下載

參數(shù)資料

| 型號: | RH80532NC025256 |

| 元件分類: | 微處理器 |

| 英文描述: | Microprocessor |

| 中文描述: | 微處理器 |

| 文件頁數(shù): | 83/93頁 |

| 文件大?。?/td> | 2353K |

| 代理商: | RH80532NC025256 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁當前第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁

Mobile Intel

Pentium

4 Processor-M Datasheet

250686-002

Datasheet

83

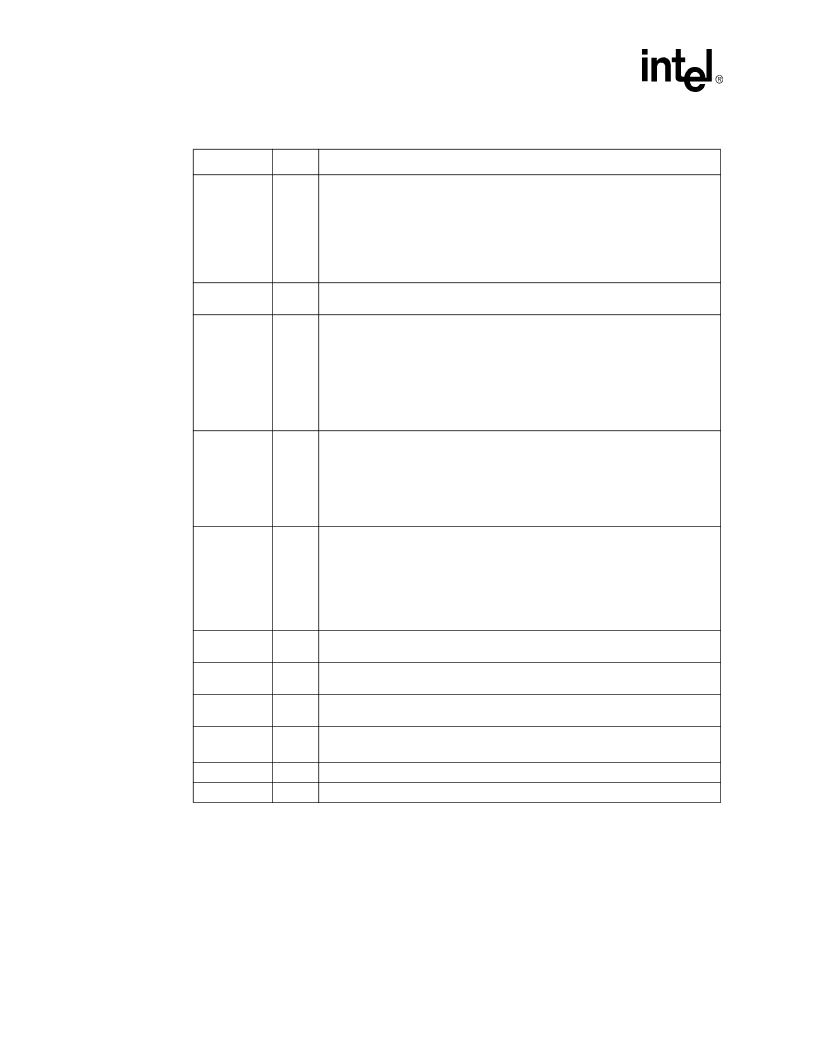

RSP#

Input

RSP# (Response Parity) is driven by the response agent (the agent responsible for

completion of the current transaction) during assertion of RS[2:0]#, the signals for

which RSP# provides parity protection. It must connect to the appropriate pins of all

processor system bus agents.

A correct parity signal is high if an even number of covered signals are low and low

if an odd number of covered signals are low. While RS[2:0]# = 000, RSP# is also

high, since this indicates it is not being driven by any agent guaranteeing correct

parity.

SKTOCC#

Output

SKTOCC# (Socket Occupied) will be pulled to ground by the processor. System

board designers may use this pin to determine if the processor is present.

SLP#

Input

SLP# (Sleep), when asserted in Stop-Grant state, causes the processor to enter the

Sleep state. During Sleep state, the processor stops providing internal clock signals

to all units, leaving only the Phase-Locked Loop (PLL) still operating. Processors in

this state will not recognize snoops or interrupts. The processor will only recognize

the assertion of the RESET# signal, deassertion of SLP#, and assertion of DPSLP#

input while in Sleep state. If SLP# is deasserted, the processor exits Sleep state

and returns to Stop-Grant state, restarting its internal clock signals to the bus and

processor core units. If DPSLP# is asserted while in the Sleep state, the processor

will exit the Sleep state and transition to the Deep Sleep state.

SMI#

Input

SMI# (System Management Interrupt) is asserted asynchronously by system logic.

On accepting a System Management Interrupt, the processor saves the current

state and enter System Management Mode (SMM). An SMI Acknowledge

transaction is issued, and the processor begins program execution from the SMM

handler.

If SMI# is asserted during the deassertion of RESET# the processor will tristate its

outputs.

STPCLK#

Input

Assertion of STPCLK# (Stop Clock) causes the processor to enter a low power

Stop-Grant state. The processor issues a Stop-Grant Acknowledge transaction, and

stops providing internal clock signals to all processor core units except the system

bus and APIC units. The processor continues to snoop bus transactions and

service interrupts while in Stop-Grant state. When STPCLK# is deasserted, the

processor restarts its internal clock to all units and resumes execution. The

assertion of STPCLK# has no effect on the bus clock; STPCLK# is an

asynchronous input.

TCK

Input

TCK (Test Clock) provides the clock input for the processor Test Bus (also known

as the Test Access Port).

TDI

Input

TDI (Test Data In) transfers serial test data into the processor. TDI provides the

serial input needed for JTAG specification support.

TDO

Output

TDO (Test Data Out) transfers serial test data out of the processor. TDO provides

the serial output needed for JTAG specification support.

TESTHI[10:8]

TESTHI[5:0]

Input

TESTHI[10:8] and TESTHI[5:0] must be connected to a V

CC

power source through

a resistor for proper processor operation. See

Section 2.5

THERMDA

Other

Thermal Diode Anode. See Section 6.

THERMDC

Other

Thermal Diode Cathode. See Section 6.

Table 36. Signal Description (Page 7 of 8)

Name

Type

Description

相關PDF資料 |

PDF描述 |

|---|---|

| RH80532NC029256 | Microprocessor |

| RH80532NC033256 | Microprocessor |

| RHE070 | Poly Switch PTC DEVICES |

| RHE1000 | Poly Switch PTC DEVICES |

| RHE1300 | Poly Switch PTC DEVICES |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| RH80532NC029256 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| RH80532NC033256 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| RH80532NC049256 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| RH80532NC049256S L8SB | 制造商:Intel 功能描述:INTEL CELERON PROCESSOR AVAILABLE AT 1.60 GHZ, 1.8 GHZ, 2.00 GHZ, 2.2 GHZ |

| RH80532NC049256S-L8SB | 制造商:Intel 功能描述:INTEL CELERON PROCESSOR AVAILABLE AT 1.60 GHZ, 1.8 GHZ, 2.00 GHZ, 2.2 GHZ |

發(fā)布緊急采購,3分鐘左右您將得到回復。