- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373273 > RH80532NC025256 Microprocessor PDF資料下載

參數(shù)資料

| 型號: | RH80532NC025256 |

| 元件分類: | 微處理器 |

| 英文描述: | Microprocessor |

| 中文描述: | 微處理器 |

| 文件頁數(shù): | 90/93頁 |

| 文件大小: | 2353K |

| 代理商: | RH80532NC025256 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁當(dāng)前第90頁第91頁第92頁第93頁

Mobile Intel

Pentium

4 Processor-M

90

Datasheet

250686-002

The system can generate a STPCLK# while the processor is in the AutoHALT Powerdown state.

When the system deasserts the STPCLK# interrupt, the processor will return execution to the

HALT state.

While in AutoHALT Powerdown state, the processor will process bus snoops.

7.2.3

Stop-Grant State

When the STPCLK# pin is asserted, the Stop-Grant state of the processor is entered 20 bus clocks

after the response phase of the processor issued Stop Grant Acknowledge special bus cycle.

Since the AGTL+ signal pins receive power from the system bus, these pins should not be driven

(allowing the level to return to V

CC

) for minimum power drawn by the termination resistors in this

state. In addition, all other input pins on the system bus should be driven to the inactive state.

BINIT# will not be serviced while the processor is in Stop-Grant state. The event will be latched

and can be serviced by software upon exit from the Stop-Grant state.

RESET# will cause the processor to immediately initialize itself, but the processor will stay in

Stop-Grant state. A transition back to the Normal state will occur with the de-assertion of the

STPCLK# signal. When re-entering the Stop-Grant state from the Sleep state, STPCLK# should

only be de-asserted one or more bus clocks after the de-assertion of SLP#.

A transition to the HALT/Grant Snoop state will occur when the processor detects a snoop on the

system bus (see

Section 7.2.4

). A transition to the Sleep state (see

Section 7.2.5

) will occur with the

assertion of the SLP# signal.

While in the Stop-Grant State, SMI#, INIT#, BINIT# and LINT[1:0] will be latched by the

processor, and only serviced when the processor returns to the Normal State. Only one occurrence

of each event will be recognized upon return to the Normal state.

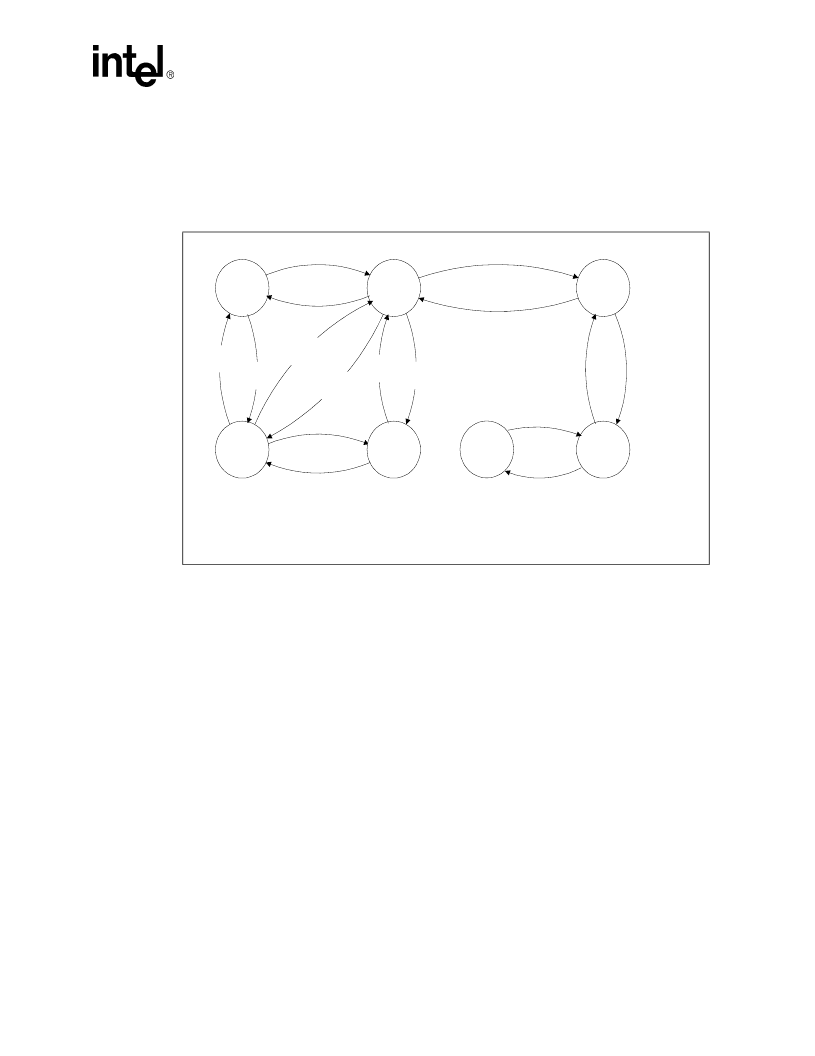

Figure 35. Clock Control States

snoop

occurs

Stop

Grant

Normal

Sleep

HALT/

Grant

Snoop

Auto Halt

Deep

Sleep

STPCLK# asserted

SLP# asserted

SLP# de-asserted

STPCLK# de-asserted

snoop

serviced

HLT

instruction

ssnoop

occurs

DPSLP#

de-asserted

DPSLP#

asserted

STPCLK#

asserted

STPCLK#

de-asserted

halt

break

V0001-04

core voltage raised

core voltage lowered

Deeper

Sleep

Halt break - A20M#, BINIT#, INIT#, INTR, NMI, PREQ#, RESET#, SMI#, or APIC interrupt

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RH80532NC029256 | Microprocessor |

| RH80532NC033256 | Microprocessor |

| RHE070 | Poly Switch PTC DEVICES |

| RHE1000 | Poly Switch PTC DEVICES |

| RHE1300 | Poly Switch PTC DEVICES |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RH80532NC029256 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| RH80532NC033256 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| RH80532NC049256 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| RH80532NC049256S L8SB | 制造商:Intel 功能描述:INTEL CELERON PROCESSOR AVAILABLE AT 1.60 GHZ, 1.8 GHZ, 2.00 GHZ, 2.2 GHZ |

| RH80532NC049256S-L8SB | 制造商:Intel 功能描述:INTEL CELERON PROCESSOR AVAILABLE AT 1.60 GHZ, 1.8 GHZ, 2.00 GHZ, 2.2 GHZ |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。