- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378193 > RS5C372A (RICOH COMPANY LTD) I2C bus SERIAL INTERFACE REAL-TIME CLOCK ICs PDF資料下載

參數(shù)資料

| 型號: | RS5C372A |

| 廠商: | RICOH COMPANY LTD |

| 元件分類: | XO, clock |

| 英文描述: | I2C bus SERIAL INTERFACE REAL-TIME CLOCK ICs |

| 中文描述: | 0 TIMER(S), REAL TIME CLOCK, PDSO8 |

| 封裝: | SSOP-8 |

| 文件頁數(shù): | 27/59頁 |

| 文件大?。?/td> | 442K |

| 代理商: | RS5C372A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁

RS5C372A/B

23

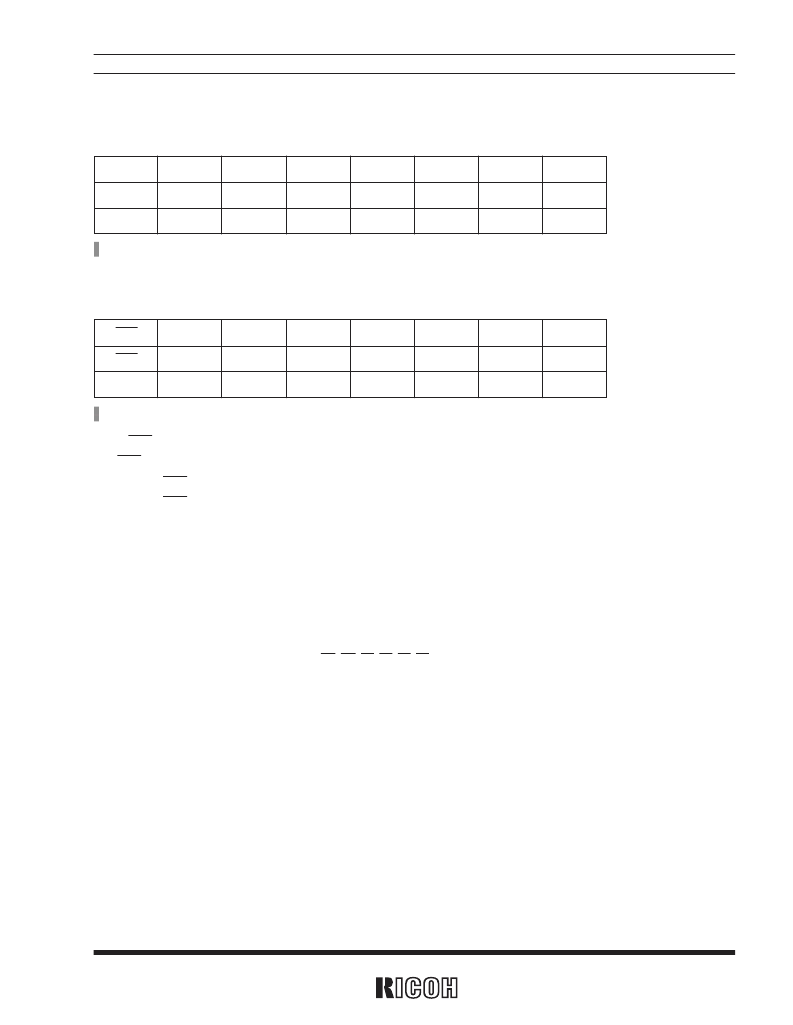

2.5-3 Year digit register (at internal address 6h)

D7

D6

D5

D4

D3

D2

D1

D0

Y

80

Y

40

Y

20

Y

10

Y

8

Y

4

Y

2

Y

1

Y

80

Y

40

Y

20

Y

10

Y

8

Y

4

Y

2

Y

1

Undefined Undefined Undefined Undefined Undefined Undefined Undefined Undefined

(For write operation)

(For read operation)

Default*

2.6 Time Trimming Register (at internal address 7h)

D7

D6

D5

D4

D3

D2

D1

D0

XSL

F

6

F

5

F

4

F

3

F

2

F

1

F

0

XSL

F

6

F

5

F

4

F

3

F

2

F

1

F

0

0

0

0

0

0

0

0

0

(For write operation)

(For read operation)

Default*

*

) The default means read value when XSTP bit is set to “1” by starting up from 0V, or supply voltage drop, etc.

2.6-1 XSL bit

The XSL bit is used to select a crystal oscillator.

Set the XSL to “0” (default) to use 32.768kHz.

Set the XSL to “1” to use 32.000kHz.

2.6-2 F

6

to F

0

The time trimming circuit adjust one second count based on this register readings when second digit is 00, 20, or 40

seconds. Normally, counting up to seconds is made once per 32,768 of clock pulse (or 32,000 when 32.000kHz crys-

tal is used) generated by the oscillator. Setting data to this register activates the time trimming circuit.

Register counts will be incremented as ((F

5

, F

4

, F

3

, F

2

, F

1

, F

0

)–1)

×

2 when F

6

is set to “0”.

Register counts will be decremented as ((F

5

, F

4

, F

3

, F

2

, F

1

, F

0

)+1)

×

2 when F

6

is set to “1”.

Counts will not change when (F

6

, F

5

, F

4

, F

3

, F

2

, F

1

, F

0

) are set to (

*

, 0, 0, 0, 0, 0,

*

).

For example, when 32.768kHz crystal is used.

When (F

6

, F

5

, F

4

, F

3

, F

2

, F

1

, F

0

) are set to (0, 0, 0, 0, 1, 1, 1), counts will change as: 32,768+(7–1)

×

2=32,780

(clock will be delayed) when second digit is 00, 20, or 40.

When (F

6

, F

5

, F

4

, F

3

, F

2

, F

1

, F

0

) are set to (0, 0, 0, 0, 0, 0, 1), counts will remain 32,768 without changing when

second digit is 00, 20, or 40.

When (F

6

, F

5

, F

4

, F

3

, F

2

, F

1

, F

0

) are set to (1, 1, 1, 1, 1, 1, 0), counts will change as: 32,768+(–2)

×

2=32,764

(clock will be advanced) when second digit is 00, 20, or 40.

Adding 2 clock pulses every 20 seconds: 2/(32,768

×

20)=3.051ppm (or 3.125ppm when 32.000kHz crystal is used),

delays the clock by approx. 3ppm. Likewise, decrementing 2 clock pulses advances the clock by 3ppm. Thus the

clock may be adjusted to the precision of ±1.5ppm. Note that the time trimming function only adjust clock timing

and oscillation frequency and 32-kHz clock output is not adjusted.

*

) The default means read value when XSTP bit is set to “1” by starting up from 0V, or supply voltage drop, etc.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RS5C372B | I2C-bus Serial Interface Real Time Clock (8pin SSOP) |

| RS5C372B-E1 | I2C-bus Serial Interface Real Time Clock (8pin SSOP) |

| RS5C372B-E2 | I2C-bus Serial Interface Real Time Clock (8pin SSOP) |

| RS5C62 | REAL-TIME CLOCK |

| RSBL-9-S | Using Permanent Magnet, High sensitivity Two Poles Signal Relay RSB RELAYS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RS5C372B | 制造商:RICOH 制造商全稱:RICOH electronics devices division 功能描述:I2C-bus Serial Interface Real Time Clock (8pin SSOP) |

| RS5C372B-E1 | 制造商:RICOH 制造商全稱:RICOH electronics devices division 功能描述:I2C-bus Serial Interface Real Time Clock (8pin SSOP) |

| RS5C372B-E2 | 制造商:RICOH 制造商全稱:RICOH electronics devices division 功能描述:I2C-bus Serial Interface Real Time Clock (8pin SSOP) |

| RS5C373A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Real-Time Clock |

| RS5C4FC | 制造商:Dialight 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。