- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376329 > RTL8100C (Electronic Theatre Controls, Inc.) SINGLE-CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT PDF資料下載

參數(shù)資料

| 型號: | RTL8100C |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | SINGLE-CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| 中文描述: | 單芯片快速以太網(wǎng)控制器電源管理 |

| 文件頁數(shù): | 50/73頁 |

| 文件大小: | 652K |

| 代理商: | RTL8100C |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁當(dāng)前第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁

RTL8100C & RTL8100CL

Datasheet

Single-Chip Fast Ethernet Controller

42

Track ID: JATR-1076-21 Rev. 1.06

RID: Revision ID Register

The Revision ID register is an 8-bit register that specifies the RTL8100C(L) controller revision number.

PIFR: Programming Interface Register

The programming interface register is an 8-bit register that identifies the programming interface of the

RTL8100C(L) controller.

PIFR = 00h (the PCI version 2.1 specification does not define any specific value for network devices).

SCR: Sub-Class Register

The Sub-class register is an 8-bit register that identifies the function of the RTL8100C(L).

SCR = 00h indicates that the RTL8100C(L) is an Ethernet controller.

BCR: Base-Class Register

The Base-Class Register is an 8-bit register that broadly classifies the function of the RTL8100C(L).

BCR = 02h indicates that the RTL8100C(L) is a network controller.

CLS: Cache Line Size

Reads will return a 0, writes are ignored.

LTR: Latency Timer Register

Specifies, in units of PCI bus clocks, the value of the latency timer of the RTL8100C(L).

When the RTL8100C(L) asserts FRAMEB, its latency timer starts to count. If the RTL8100C(L) deasserts

FRAMEB prior to count expiration, the contents of the latency timer are ignored. Otherwise, after the count

expires, the RTL8100C(L) initiates transaction termination as soon as its GNTB is deasserted. Software is able

to read or write, and the default value is 00H.

HTR: Header Type Register

Reads will return a 0, writes are ignored.

BIST: Built-In Self Test

Reads will return a 0, writes are ignored.

IOAR: Input Output Address Register

This register specifies the base IO address that is required to build an address map during configuration. It

also specifies the number of bytes required as well as an indication that it can be mapped into IO space.

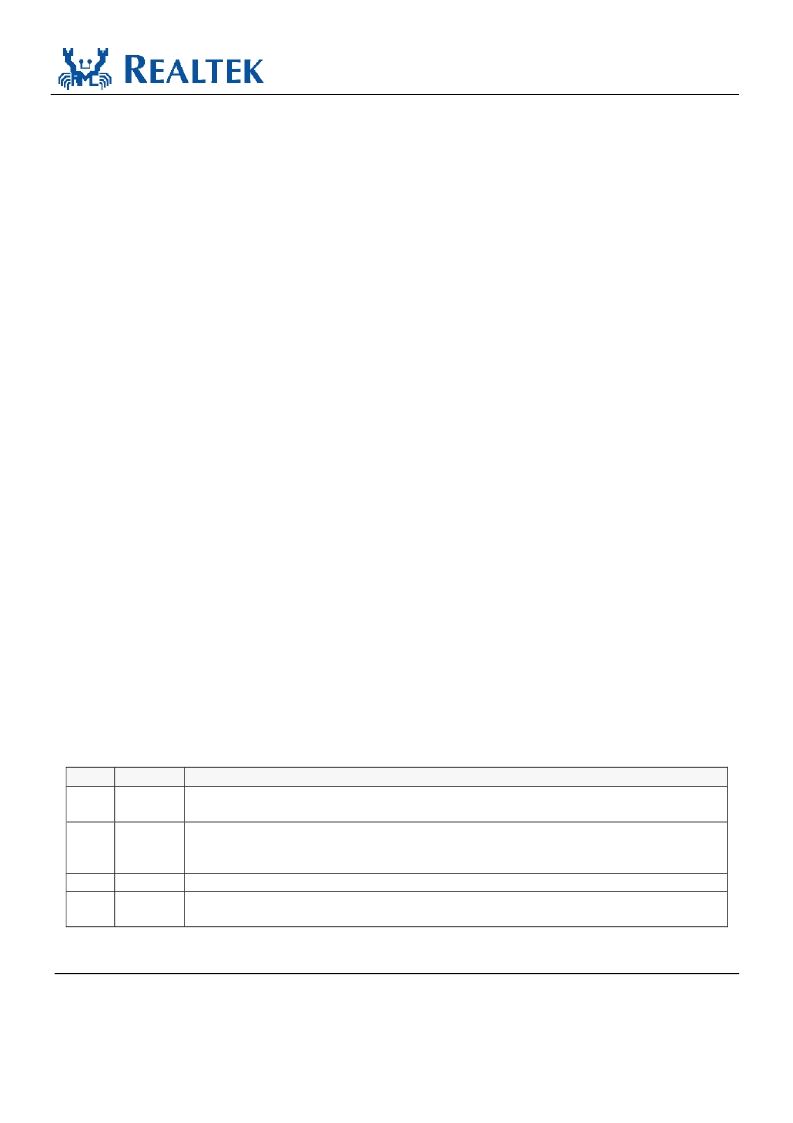

Table 43. Base IO Address

Bit

31-8

Symbol

IOAR31-8 Base IO Address.

This is set by software to the base IO address for the operational register map.

IOSIZE

IO Size.

Read back as 0. This allows the PCI bridge to determine that the RTL8100C(L) requires 256 bytes of

IO space.

-

Reserved.

IOIN

IO Space Indicator.

Read only. Set to 1 by the RTL8100C(L) to indicate that it is capable of being mapped into IO space.

Description

7-2

1

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RTL8100C-LF | SINGLE-CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8100CL | SINGLE-CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8130 | REALTEK SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8100 | REALTEK SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8100B | REALTEK SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RTL8100CL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE-CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8100C-LF | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE-CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8100CL-LF | 制造商:Realtek Semiconductor 功能描述:RTL8100CL Series 3.6 V Fast Ethernet Controller with Power Management LQFP-128 |

| RTL8100L | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:REALTEK SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8101 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:REALTEK SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。