- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378205 > RTL8139C (Electronic Theatre Controls, Inc.) REALTEK 3.3V SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT PDF資料下載

參數(shù)資料

| 型號(hào): | RTL8139C |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | REALTEK 3.3V SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| 中文描述: | 瑞昱3.3V的單芯片快速以太網(wǎng)控制器電源管理 |

| 文件頁數(shù): | 17/62頁 |

| 文件大?。?/td> | 648K |

| 代理商: | RTL8139C |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁

RTL8139C(L)

2002/01/10

Rev.1.4

17

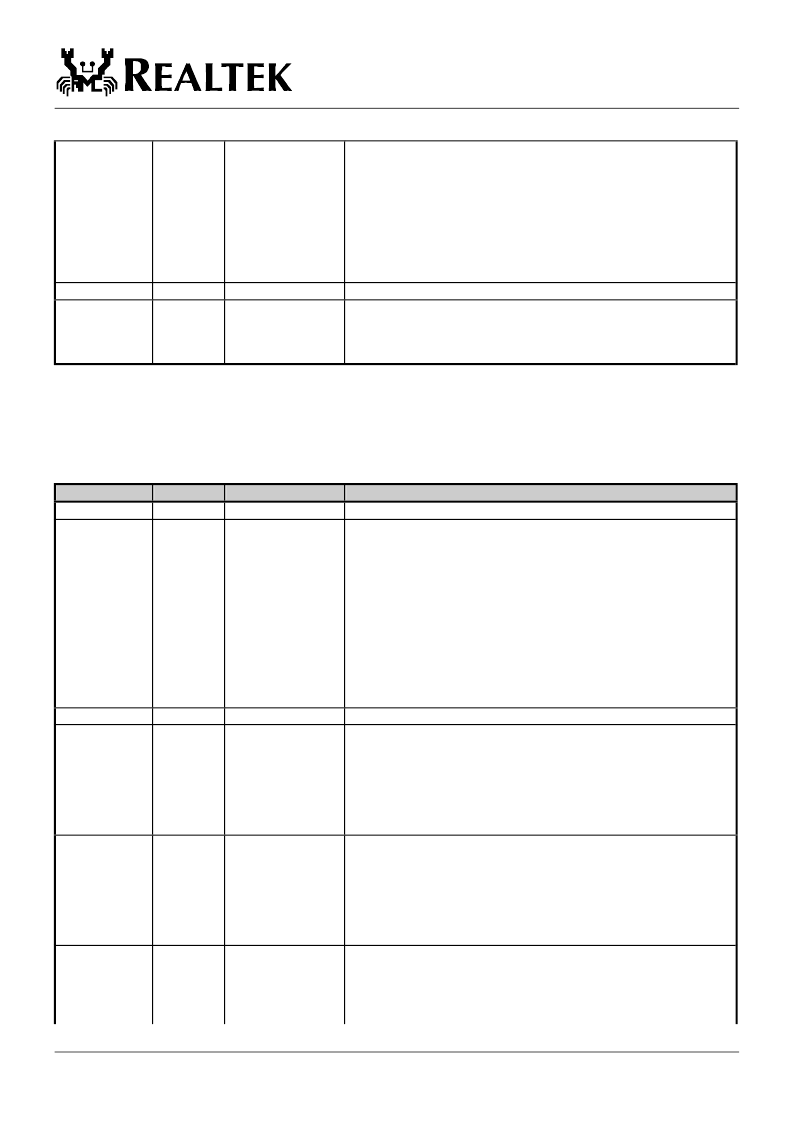

7-4

R/W

TXRR

Tx Retry Count:

These are used to specify additional transmission

retries in multiples of 16 (IEEE 802.3 CSMA/CD retry count). If the

TXRR is set to 0, the transmitter will re-transmit 16 times before

aborting due to excessive collisions. If the TXRR is set to a value

greater than 0, the transmitter will re-transmit a number of times equal

to the following formula before aborting:

Total retries = 16 + (TXRR * 16)

The TER bit in the ISR register or transmit descriptor will be set when

the transmission fails and reaches to this specified retry count.

Reserved

Clear Abort:

Setting this bit to 1 causes the RTL8139C(L) to

retransmit the packet at the last transmitted descriptor when this

transmission was aborted. Setting this bit is only permitted in the

transmit abort state.

3-1

0

-

-

W

CLRABT

6.8 Receive Configuration Register

(Offset 0044h-0047h, R/W)

This register is used to set the receive configuration for the RTL8139C(L). Receive properties such as accepting error packets,

runt packets, setting the receive drain threshold etc. are controlled here.

Bit

31-28

27-24

R/W

-

R/W

Symbol

-

ERTH3, 2, 1, 0

Description

Reserved

Early Rx threshold bits:

These bits are used to select the Rx threshold

multiplier of the whole packet that has been transferred to the system

buffer in early mode when the frame protocol is under the

RTL8139C(L)'s definition.

0000 = no early rx threshold

0010 = 2/16

0100 = 4/16

0110 = 6/16

1000 = 8/16

1010 = 10/16

1100 = 12/16

1110 = 14/16

Reserved

Multiple early interrupt select:

When this bit is set, any received

packet invokes early interrupt according to MULINT<MISR[11:0]>

setting in early mode. When this bit is reset, the packets of familiar

protocol (IPX, IP, NDIS, etc) invoke early interrupt according to

RCR<ERTH[3:0]> setting in early mode. The packets of unfamiliar

protocol will invoke early interrupt according to the setting of

MULINT<MISR[11:0]>.

The RTL8139C(L) receives the error packet whose length is larger than

8 bytes after setting the RER8 bit to 1.

The RTL8139C(L) receives the error packet larger than 64-byte long

when the RER8 bit is cleared. The power-on default is zero.

If AER or AR is set, the RER will be set when the RTL8139C(L)

receives an error packet whose length is larger than 8 bytes. The RER8

is “ Don’t care “ in this situation.

Rx FIFO Threshold:

Specifies Rx FIFO Threshold level. When the

number of the received data bytes from a packet, which is being

received into the RTL8139C(L)'s Rx FIFO, has reached to this level (or

the FIFO has contained a complete packet), the receive PCI bus master

function will begin to transfer the data from the FIFO to the host

0001 = 1/16

0011 = 3/16

0101 = 5/16

0111 = 7/16

1001 = 9/16

1011 = 11/16

1101 = 13/16

1111 = 15/16

23-18

17

-

-

R/W

MulERINT

16

R/W

RER8

15-13

R/W

RXFTH2, 1, 0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RTL8139L | REALTEK 3.3V SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139 | REALTEK 3.3V SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139A | REALTEK SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139B | REALTEK SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139D | REALTEK SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RTL8139C_PLUS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:RTL8139C_Plus Specification |

| RTL8139CL | 制造商:Realtek Semiconductor 功能描述: |

| RTL8139CL+ | 制造商:Realtek Semiconductor 功能描述: |

| RTL8139D | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE-CHIP MULTI-FUNCTION 10/100Mbps ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139D(L) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:RTL8139D(L) Specification |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。