- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376330 > S12MSCANV2D (Motorola, Inc.) MC9S12DT128 Device User Guide V02.09 PDF資料下載

參數(shù)資料

| 型號: | S12MSCANV2D |

| 廠商: | Motorola, Inc. |

| 英文描述: | MC9S12DT128 Device User Guide V02.09 |

| 中文描述: | MC9S12DT128設備的用戶手冊V02.09 |

| 文件頁數(shù): | 81/138頁 |

| 文件大小: | 2083K |

| 代理商: | S12MSCANV2D |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁當前第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁

MC9S12DT128 Device User Guide — V02.09

81

Section 5 Resets and Interrupts

5.1 Overview

Consult the Exception Processing section of the CPU Reference Manual for information on resets and

interrupts.

5.2 Vectors

5.2.1 Vector Table

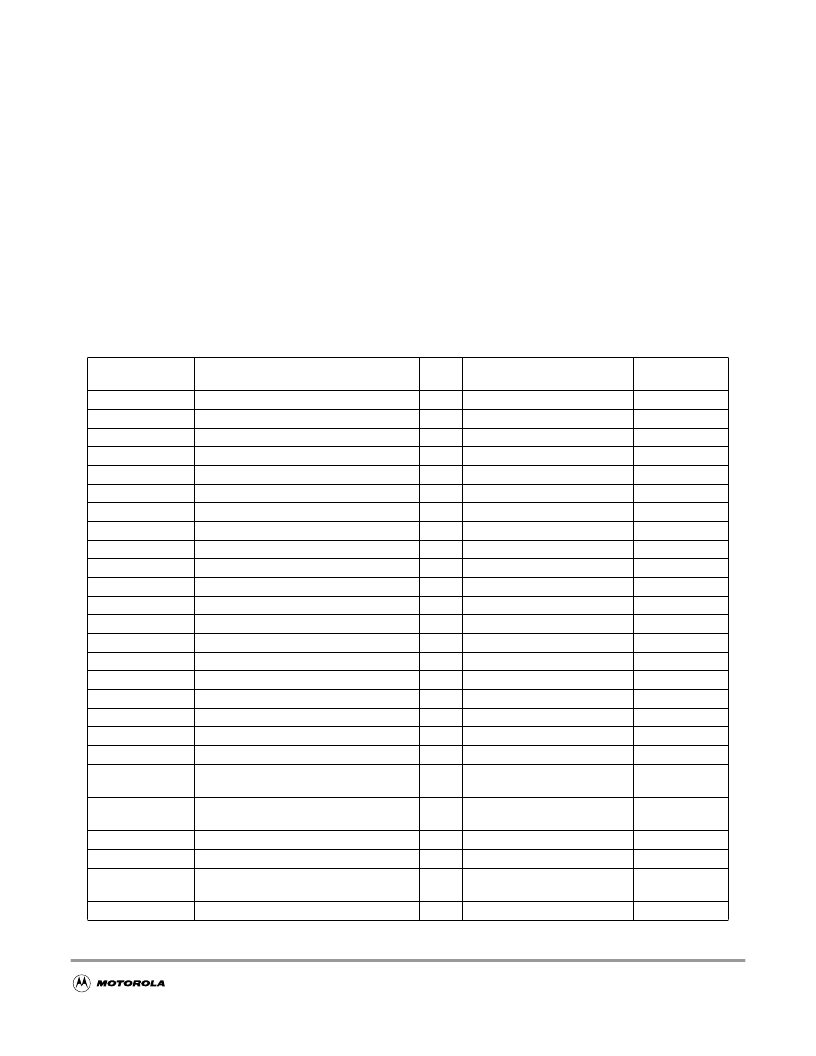

Table 5-1

lists interrupt sources and vectors in default order of priority.

Table 5-1 Interrupt Vector Locations

Vector Address

Interrupt Source

CCR

Mask

None

None

None

None

None

X-Bit

I-Bit

I-Bit

I-Bit

I-Bit

I-Bit

I-Bit

I-Bit

I-Bit

I-Bit

I-Bit

I-Bit

I-Bit

I-Bit

I-Bit

Local Enable

HPRIO Value

to Elevate

–

–

–

–

–

–

$F2

$F0

$EE

$EC

$EA

$E8

$E6

$E4

$E2

$E0

$DE

$DC

$DA

$D8

$FFFE, $FFFF

$FFFC, $FFFD

$FFFA, $FFFB

$FFF8, $FFF9

$FFF6, $FFF7

$FFF4, $FFF5

$FFF2, $FFF3

$FFF0, $FFF1

$FFEE, $FFEF

$FFEC, $FFED

$FFEA, $FFEB

$FFE8, $FFE9

$FFE6, $FFE7

$FFE4, $FFE5

$FFE2, $FFE3

$FFE0, $FFE1

$FFDE, $FFDF

$FFDC, $FFDD

$FFDA, $FFDB

$FFD8, $FFD9

Reset

None

Clock Monitor fail reset

COP failure reset

Unimplemented instruction trap

SWI

XIRQ / BF High Priority Sync Pulse

IRQ

Real Time Interrupt

Enhanced Capture Timer channel 0

Enhanced Capture Timer channel 1

Enhanced Capture Timer channel 2

Enhanced Capture Timer channel 3

Enhanced Capture Timer channel 4

Enhanced Capture Timer channel 5

Enhanced Capture Timer channel 6

Enhanced Capture Timer channel 7

Enhanced Capture Timer overflow

Pulse accumulator A overflow

Pulse accumulator input edge

SPI0

COPCTL (CME, FCME)

COP rate select

None

None

None / BFRIER (XSYNIE)

INTCR (IRQEN)

CRGINT (RTIE)

TIE (C0I)

TIE (C1I)

TIE (C2I)

TIE (C3I)

TIE (C4I)

TIE (C5I)

TIE (C6I)

TIE (C7I)

TSCR2 (TOF)

PACTL (PAOVI)

PACTL (PAI)

SPICR1 (SPIE, SPTIE)

SCICR2

(TIE, TCIE, RIE, ILIE)

SCICR2

(TIE, TCIE, RIE, ILIE)

ATDCTL2 (ASCIE)

ATDCTL2 (ASCIE)

PIEJ

(PIEJ7, PIEJ6, PIEJ1, PIEJ0)

PIEH (PIEH7-0)

$FFD6, $FFD7

SCI0

I-Bit

$D6

$FFD4, $FFD5

SCI1

I-Bit

$D4

$FFD2, $FFD3

$FFD0, $FFD1

ATD0

ATD1

I-Bit

I-Bit

$D2

$D0

$FFCE, $FFCF

Port J

I-Bit

$CE

$FFCC, $FFCD

Port H

I-Bit

$CC

相關PDF資料 |

PDF描述 |

|---|---|

| S20100 | Silicon Power Rectifier |

| S20120 | Silicon Power Rectifier |

| S2020 | Silicon Power Rectifier |

| S2040 | Silicon Power Rectifier |

| S204 | Silicon Power Rectifier |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| S12N11F-A | 制造商:TE Connectivity 功能描述: |

| S12N2.5A-G | 制造商:TE Connectivity 功能描述: |

| S12N2A-G1 | 制造商:TE Connectivity 功能描述: |

| S12N3W3C | 制造商:HB 制造商全稱:HB Electronic Components 功能描述:LED |

| S12N3W6C | 制造商:HB 制造商全稱:HB Electronic Components 功能描述:LED |

發(fā)布緊急采購,3分鐘左右您將得到回復。