- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98229 > THS8083APZPG4 (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP100 PDF資料下載

參數(shù)資料

| 型號: | THS8083APZPG4 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 封裝: | GREEN, PLASTIC, HTQFP-100 |

| 文件頁數(shù): | 42/63頁 |

| 文件大小: | 320K |

| 代理商: | THS8083APZPG4 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁當前第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁

64

6.4.4

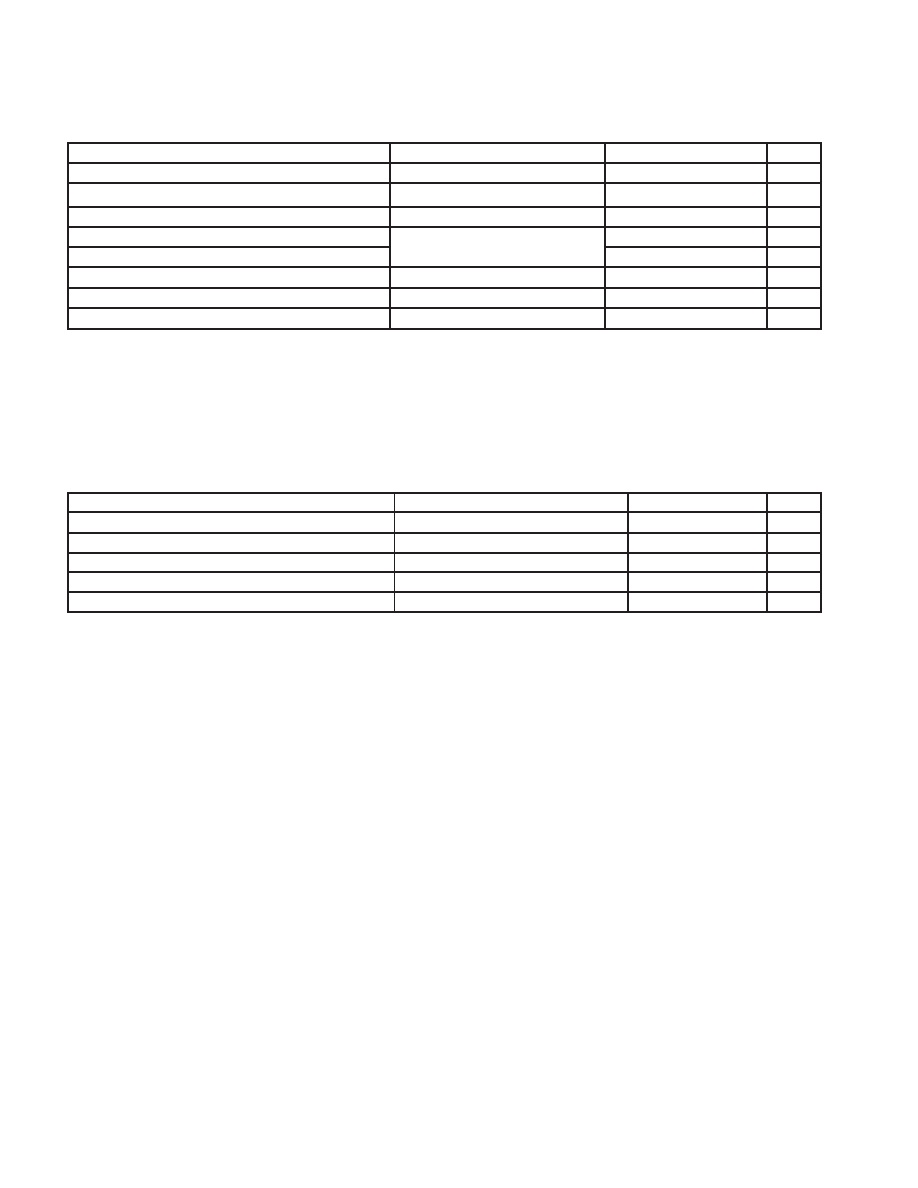

I2C Interface

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

VIL

Low-level input voltage

0.99

V

VIH

High-level input voltage

2.31

V

f(SCL)

SCL clock frequency

0

400/100

kHz

t(LOW)

Low period of SCL

Valid for I2C fast mode support only.

1.3

s

t(HIGH)

High period of SCL

Valid for I2C fast mode support only.

See footnotes to SCL clock frequency.

0.6

s

th(DATA)

Data hold time

0§

s

tsu(DATA)

Data setup time

100

s

C(b)

Capacitive load for each bus line#

400

pF

For DTO clock frequencies 25 MHz minimum (I2C fast mode)

For DTO clock frequencies below 25 MHz (I2C normal mode)

§ The device must internally provide a hold time of 300 ns for the SDA signal (referred to VIH(min) of the SCL signal) in order to bridge the undefined

region of the falling edge of SCL.

If the device is used in a standard mode I2C system, the requirement of tsu(DATA)>=250 ns must be met.

# Cb= total capacitance of one bus line in pF

6.4.5

ADC Channel

6.4.5.1 DC Accuracy

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

Integral nonlinearity (INL)

PLL (see Note 7)

2

±1

2

LSB

Integral nonlinearity (INL)

PLL (see Note 7)

2

±1

2

LSB

Differential nonlinearity (DNL)

PLL (see Note 8)

1

1.5

LSB

Differential nonlinearity (DNL)

PLL (see Note 8)

1

1.5

LSB

No missing codes

Assured

Gain error

ADC_INTREF (see Note 9)

60

mV

Offset error

ADC_INTREF (see Note 10)

60

mV

Assured at nominal voltage supply levels only.

NOTES:

7. Integral nonlinearity (INL) —Integral nonlinearity refers to the deviation of each individual code from a line drawn from zero to full

scale. The point used as zero occurs 1/2 LSB before the first code transition. The full-scale point is defined as a level 1/2 LSB beyond

the last code transition. The deviation is measured from the center of each particular code to the true straight line between these

two end points.

8. Differential nonlinearity (DNL)—An ideal ADC exhibits code transitions that are exactly 1 LSB apart. DNL is the deviation from this

ideal value. Therefore, this measure indicates how uniform the transfer function step sizes are. The ideal step size is defined here

as the step size for the device under test (i.e., last transition level first transition level)/(2n 2). Using this definition for DNL

separates the effects of gain and offset error. A DNL of less than

±1 LSB ensures no missing codes. A DNL of less than ±1/2 LSB

assures monotonic behavior.

9. Gain error—The first code transition should occur for an analog value 1/2 LSB above nominal negative full scale (the voltage applied

to the REFBI terminal). The last transition should occur for an analog value 1/2 LSB below nominal positive full scale (the voltage

applied to the REFTI terminal). Gain error is defined here as the deviation from the ideal location of the highest transition level on

the ADC transfer function.

10. Offset error—The first code transition should occur at a level 1/2 LSB above zero. Offset is defined as the deviation of the actual

first code transition from that point.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| THS8083CPZP | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| THS8133ACPHP | PARALLEL, WORD INPUT LOADING, 0.005 us SETTLING TIME, 10-BIT DAC, PQFP48 |

| THS8133BCPHP | PARALLEL, WORD INPUT LOADING, 0.005 us SETTLING TIME, 10-BIT DAC, PQFP48 |

| THS8133BCPHPG4 | PARALLEL, WORD INPUT LOADING, 0.005 us SETTLING TIME, 10-BIT DAC, PQFP48 |

| THS8133CPHP | PARALLEL, WORD INPUT LOADING, 0.005 us SETTLING TIME, 10-BIT DAC, PQFP48 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| THS8083CPZP | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| THS8083EVM | 制造商:Texas Instruments 功能描述:THS8083EVM - Bulk |

| THS8083T | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Triple 8-Bit, 80 MSPS, 3.3-V Video and Graphics Digitizer With Digital PLL |

| THS8-10R-D | 制造商:Thomas & Betts 功能描述:CATAMOUNT CABLE TIES |

| THS8133 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TRIPLE 10-BIT, 80 MSPS VIDEO D/A CONVERTER WITH TRI-LEVEL SYNC GENERATION WITH TRI-LEVEL SYNC GENERATION |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。