- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄383953 > TLC32040MFK (Texas Instruments, Inc.) ANALOG INTERFACE CIRCUIT PDF資料下載

參數(shù)資料

| 型號(hào): | TLC32040MFK |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | ANALOG INTERFACE CIRCUIT |

| 中文描述: | 模擬接口電路 |

| 文件頁(yè)數(shù): | 16/30頁(yè) |

| 文件大?。?/td> | 202K |

| 代理商: | TLC32040MFK |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)當(dāng)前第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)

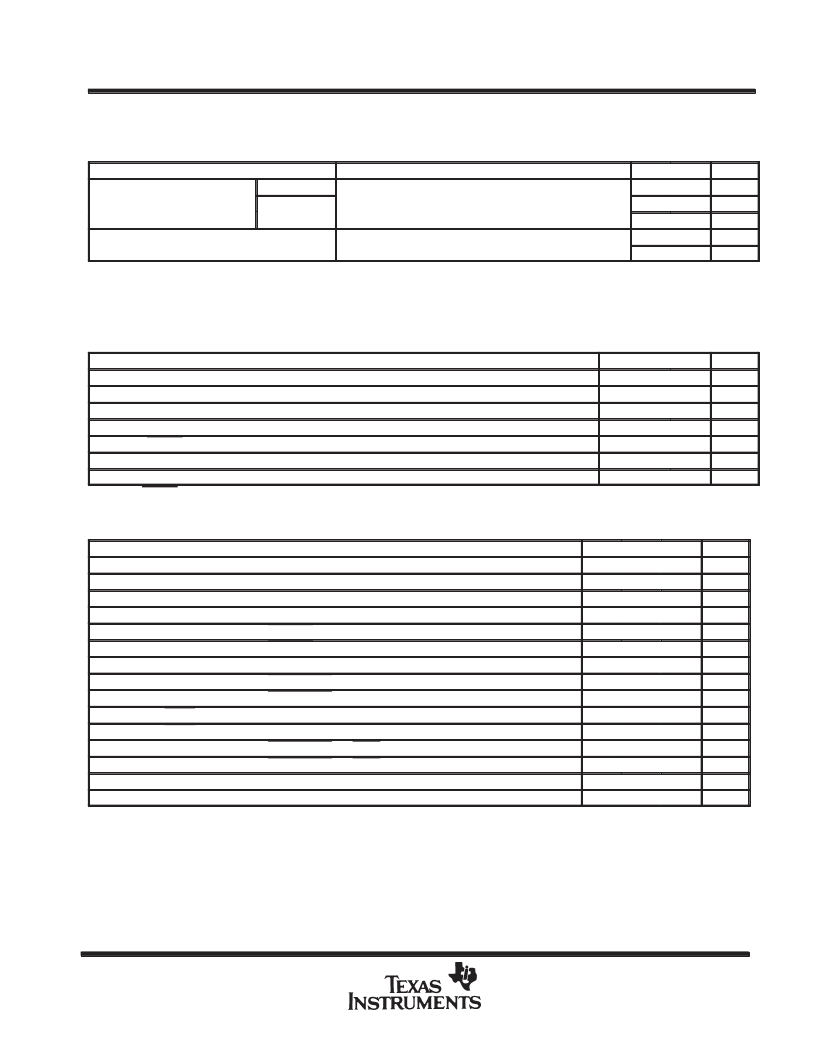

Differential

Receive noise (see Note 12)

Inputs grounded, gain = 1

TLC32040M

ANALOG INTERFACE CIRCUIT

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

4–16

operating characteristics over recommended operating free-air temperature range, V

CC+

= 5 V,

V

CC–

= –5 V, V

DD

= 5 V

noise (measurement includes low-pass and band-pass switched-capacitor filters)

PARAMETER

Single ended

Transmit noise

TEST CONDITIONS

TYP

200

300

MAX

UNIT

μ

V rms

μ

V rms

dBrnc0

μ

V rms

dBrnc0

DX input = 00000000000000, constant input code

500

20

300

20

475

NOTE 12. This noise is referred to the input with a buffer gain of one. If the buffer gain is two or four, the noise figure will be correspondingly reduced.

The noise is computed by statistically evaluating the digital output of the A/D converter.

timing requirements

serial port recommended input signals

PARAMETER

MIN

100

MAX

192

10

10

58%

UNIT

ns

ns

ns

tc(MCLK) Master clock cycle time

tr(MCLK)

Master clock rise time

tf(MCLK)

Master clock fall time

Master clock duty cycle

RESET pulse duration (see Note 13)

tsu(DX)

DX setup time before SCLK

↓

th(DX)

DX hold time before SCLK

↓

NOTE 13. RESET pulse duration is the amount of time that the reset pin is held below 0.8 V after the power supplies have reached their

recommended values.

42%

800

28

ns

ns

ns

tc(SCLK)/4

serial port – AIC output signals

PARAMETER

MIN

400

TYP

MAX

UNIT

ns

ns

ns

tc(SCLK)

tf(SCLK)

tr(SCLK)

Shift clock (SCLK) cycle time

Shift clock (SCLK) fall time

Shift clock (SCLK) rise time

Shift clock (SCLK) duty cycle

Delay from SCLK

↑

to FSR/FSX

↓

Delay from SCLK

↑

to FSR/FSX

↑

DR valid after SCLK

↑

Delay from SCLK

↑

to EODX/EODR

↓

in WORD mode

Delay from SCLK

↑

to EODX/EODR

↑

in WORD mode

EODX fall time

EODR fall time

Delay from SCLK

↑

to EODX/EODR

↓

in BYTE mode

Delay from SCLK

↑

to EODX/EODR

↑

in BYTE mode

Delay from MSTR CLK

↑

to SCLK

↓

Delay from MSTR CLK

↑

to SCLK

↓

All typical values are at TA = 25

°

C.

50

50

50%

td(CH-FL)

td(CH-FH)

td(CH-DR)

tdw(CH-EL)

tdw(CH-EH)

tf(EODX)

tf(EODR)

tdb(CH-EL)

tdb(CH-EH)

td(MH-SL)

td(MH-SH)

260

260

316

280

280

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

15

15

100

100

65

65

105

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLC32040MJ | ANALOG INTERFACE CIRCUIT |

| TLC32044C | VOICE-BAND ANALOG INTERFACE CIRCUITS |

| TLC32045IN | VOICE-BAND ANALOG INTERFACE CIRCUITS |

| TLC32044E | VOICE-BAND ANALOG INTERFACE CIRCUITS |

| TLC32044I | VOICE-BAND ANALOG INTERFACE CIRCUITS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLC32040MJ | 制造商:TI 制造商全稱(chēng):Texas Instruments 功能描述:ANALOG INTERFACE CIRCUIT |

| TLC32041C | 制造商:TI 制造商全稱(chēng):Texas Instruments 功能描述:ANALOG INTERFACE CIRCUITS |

| TLC32041CFN | 制造商:TI 制造商全稱(chēng):Texas Instruments 功能描述:ANALOG INTERFACE CIRCUITS |

| TLC32041CN | 制造商:TI 功能描述:32041 |

| TLC32041I | 制造商:TI 制造商全稱(chēng):Texas Instruments 功能描述:ANALOG INTERFACE CIRCUITS |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。