- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385939 > TMS279XN (Texas Instruments, Inc.) FLOPPY DISK FORMATTERICONTROLLER FAMILY PDF資料下載

參數(shù)資料

| 型號: | TMS279XN |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | FLOPPY DISK FORMATTERICONTROLLER FAMILY |

| 中文描述: | 軟盤驅(qū)動FORMATTERICONTROLLER家庭 |

| 文件頁數(shù): | 7/40頁 |

| 文件大?。?/td> | 334K |

| 代理商: | TMS279XN |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

TMS279X (WD279X) FLOPPY DISK FORMATTER / CONTROLLER FAMILY

7

processor interface

The interface to the processor is accomplished through the eight data access lines (DAL) and associated control

signals. The DAL are used to transfer data, status, and control words out of, or into the TMS279X. The DAL are

three-state buffers that are enabled as output drivers when chip select (CS#) and read enable (RE#) are active

(low logic state) or act as input receivers when CS# and write enable (WE#) are active.

When transfer of data with the floppy disk controller is required by the host processor, the device address is

decoded and CS# is made low. The address bits A1 and AO, combined with the signals RE# during a mad

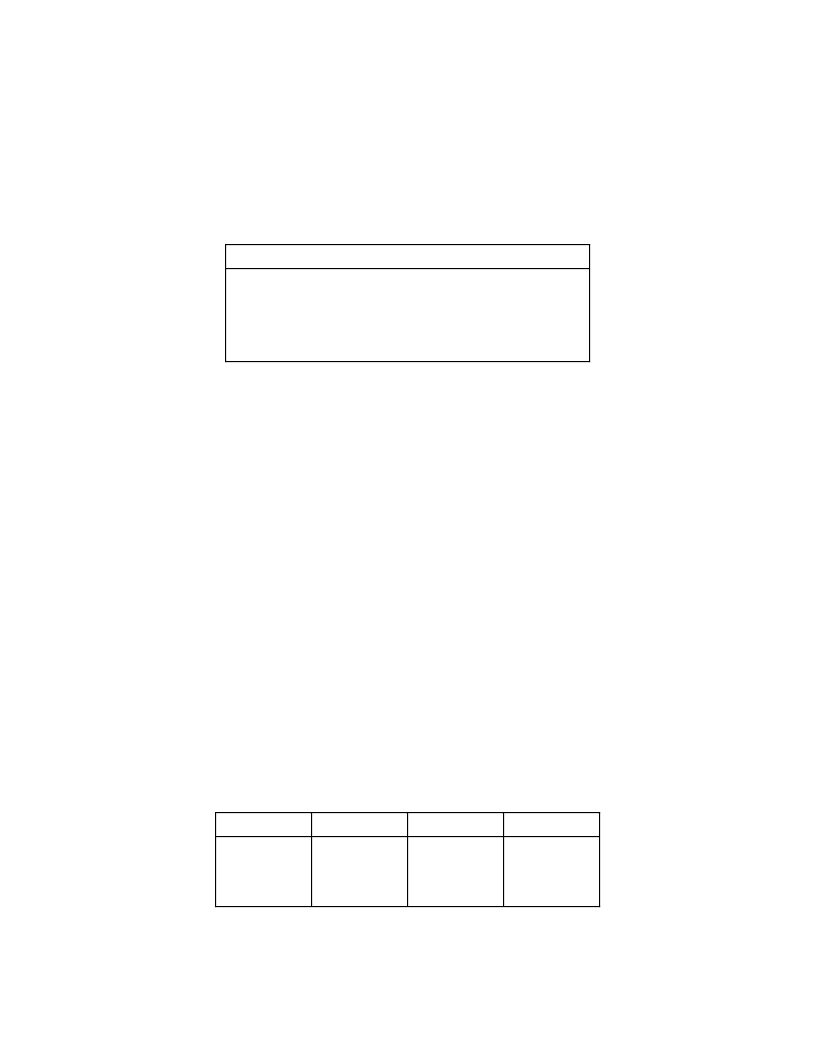

operation or WE# during a write operation are interpreted as selecting the following registers:

A1

A0

READ (RE#)

WRITE (WE#)

0

0

Status Register

Command Register

0

1

Track Register

Track Register

1

0

Sector Register

Sector Register

1

1

Data Register

Data Register

During direct memory access (DMA) types of data transfers between the data register of the TMS279X and the

processor, the data request (DRQ) output is used in data transfer control. This signal also appears as status bit 1

during read and write operations.

On disk read operations, the data request is activated (set high) when an assembled serial input byte is

transferred in parallel to the data register. This bit is cleared when the data register is read by the processor. If the

data register is read after one or more characters are lost, by having new data transferred into the register prior to

processor readout, the lost data bit is set in the status register. The read operation continues until the end of

sector is reached.

On disk write operations, the data request is activated when the data register transfers its contents to the data

shift register, and requires a new data byte. It is reset when the data register is loaded with new data by the

processor. If new data is not loaded at the time the next serial byte is required by the floppy disk, a byte of zeroes

is written on the diskette and the lost data bit is set in the status register.

At the completion of every command, an INTRQ is generated. INTRQ is reset by either reading the status register

or by loading the command register with a new command. In addition, INTRQ is generated if a Force Interrupt

command condition is met.

The 279X has two modes of operation according to the state of DDEN# (pin 37). When DDEN# = 1, single density

(FM) is selected. When DDEN# = 0, double density (MFM) is selected. In either case, the CLK input (pin 24) is set

at 2 MHz for 8" drives or 1 MHz for 5 " drives.

On the 2791/2793, the ENMF# input (pin 25) can be used for controlling both 5 " and 8" drives with a single 2

MHz clock. When ENMF# = 0, an internal ÷ 2 of the CLK is performed. When ENMF# = 1, no divide takes place.

This allows the use of a 2 MHz clock for both 5 " and 8" configurations.

The internal VCO frequency must also be set to the proper value. The 5#/8 input (pin 17) is used to select data

separator operation by internally dividing the read clock. When 5#/8 = 0, 5 " data separation is selected; when

5#/8 = 1, 8 " drive data separation is selected.

CLOCK (24)

ENMF# (25)

5#/8 (17)

DRIVE

2 MHz

1

1

8"

2 MHz

0

0

5 "

1 MHz

0

0

5 "

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMS27C040-15 | Programmable Read-Only Memory(512K×8結(jié)構(gòu),可擦可編程只讀存儲器) |

| TMS27C256-150 | Programmable Read-Only Memory(32K×8結(jié)構(gòu),可擦可編程只讀存儲器) |

| TMS27C512-150 | Programmable Read-Only Memory(64K×8結(jié)構(gòu),可擦可編程只讀存儲器) |

| TMS28F512A(中文) | Flash Electrically Erasable Programmable Read-Only Memory(64K×8結(jié)構(gòu),可擦可編程閃速只讀存儲器) |

| TMS28F512A-15C4FML(中文) | Flash Electrically Erasable Programmable Read-Only Memory(64K×8結(jié)構(gòu),可擦可編程閃速只讀存儲器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMS27C/PC256-10 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TMS27C256 32768 BY 8-BIT UV ERASABLE TMS27PC256 32768 BY 8-BIT PROGRAMMABLE READ-ONLY MEMORIES |

| TMS27C/PC256-12 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TMS27C256 32768 BY 8-BIT UV ERASABLE TMS27PC256 32768 BY 8-BIT PROGRAMMABLE READ-ONLY MEMORIES |

| TMS27C/PC256-15 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TMS27C256 32768 BY 8-BIT UV ERASABLE TMS27PC256 32768 BY 8-BIT PROGRAMMABLE READ-ONLY MEMORIES |

| TMS27C/PC256-17 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TMS27C256 32768 BY 8-BIT UV ERASABLE TMS27PC256 32768 BY 8-BIT PROGRAMMABLE READ-ONLY MEMORIES |

| TMS27C/PC256-20 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TMS27C256 32768 BY 8-BIT UV ERASABLE TMS27PC256 32768 BY 8-BIT PROGRAMMABLE READ-ONLY MEMORIES |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。