- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368672 > TMS320C240PQL 16-Bit Microcontroller PDF資料下載

參數(shù)資料

| 型號(hào): | TMS320C240PQL |

| 英文描述: | 16-Bit Microcontroller |

| 中文描述: | 16位微控制器 |

| 文件頁數(shù): | 26/105頁 |

| 文件大小: | 1481K |

| 代理商: | TMS320C240PQL |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁

TMS320C240, TMS320F240

DSP CONTROLLERS

SPRS042D – OCTOBER 1996 – REVISED NOVEMBER 1998

26

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251–1443

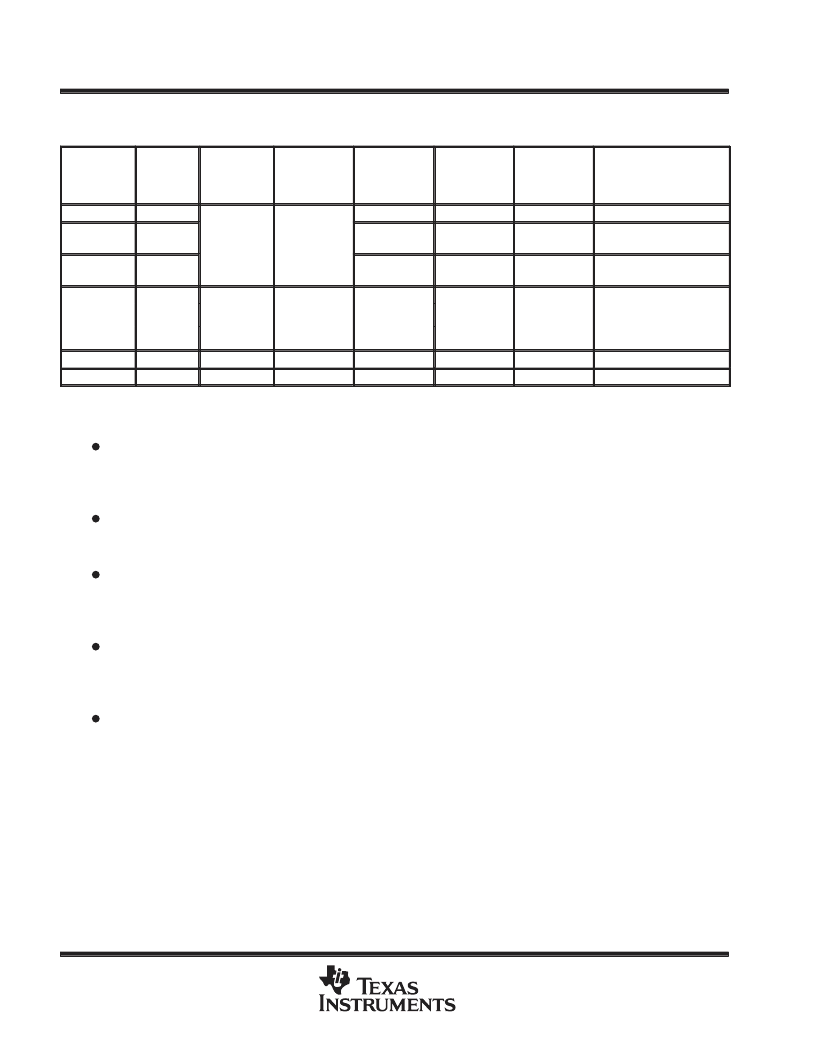

hardware-generated interrupts (continued)

Table 7. ’x240 Interrupt Locations and Priorities (Continued)

INTERRUPT

NAME

OVERALL

PRIORITY

DSP-CORE

INTERRUPT,

AND

ADDRESS

INT5

PERIPHERAL

VECTOR

ADDRESS

PERIPHERAL

VECTOR

ADDRESS

OFFSET

0005h

MASKABLE

’x240

SOURCE

PERIPHERAL

MODULE

SPI

FUNCTION

INTERRUPT

SPIINT

34

SYSIVR

(701Eh)

Y

Low-priority SPI interrupt

RXINT

35

000Ah

(System)

0006h

Y

SCI

SCI receiver interrupt

(low priority)

TXINT

36

0007h

Y

SCI

SCI transmitter interrupt

(low priority)

ADCINT

37

INT6

SYSIVR

0004h

Y

ADC

Analog-to-digital interrupt

XINT1

XINT2

XINT3

38

39

40

000Ch

(System)

(701Eh)

0001h

0011h

001Fh

Y

Y

Y

External

pins

Low-priority external

user interrupts

RESERVED

41

000Eh

N/A

Y

DSP Core

Used for analysis

TRAP

N/A

0022h

N/A

N/A

TRAP instruction vector

external interrupts

The ’x240 has five external interrupts. These interrupts include:

XINT1.

Type A interrupt. The XINT1 control register (at 7070h) provides control and status for this interrupt.

XINT1 can be used as a high-priority (Level 1) or low-priority (Level 6) maskable interrupt or as a

general-purpose input pin. XINT1 can also be programmed to trigger an interrupt on either the rising or the

falling edge.

NMI.

Type A interrupt. The NMI control register (at 7072h) provides control and status for this interrupt. NMI

is a nonmaskable external interrupt or a general-purpose input pin. NMI can also be programmed to trigger

an interrupt on either the rising or the falling edge.

XINT2.

Type C interrupt. The XINT2 control register (at 7078h) provides control and status for this interrupt.

XINT2 can be used as a high-priority (Level 1) or low-priority (Level 6) maskable interrupt or a

general-purpose I/O pin. XINT2 can also be programmed to trigger an interrupt on either the rising or the

falling edge.

XINT3.

Type C interrupt. The XINT3 control register (at 707Ah) provides control and status for this interrupt.

XINT3 can be used as a high-priority (Level 1) or low-priority (Level 6) maskable interrupt or as a

general-purpose I/O pin. XINT3 can also be programmed to trigger an interrupt on either the rising or the

falling edge.

PDPINT.

This interrupt is provided for safe operation of the power converter and motor drive. This maskable

interrupt can put the timers and PWM output pins in the high-impedance state and inform the CPU in case

of motor drive abnormalities such as overvoltage, overcurrent, and excessive temperature rise. PDPINT is

a Level 2 interrupt.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMS320C240PQQ | 16-Bit Microcontroller |

| TMS320F240PQL | 16-Bit Microcontroller |

| TMS320F240PQQ | 16-Bit Microcontroller |

| TMS320F240PQS | 16-Bit Microcontroller |

| TMS320LC31-40 | Digital Signal Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMS320C240PQQ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Microcontroller |

| TMS320C241 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Digital Signal Processor |

| TMS320C241FNS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Digital Signal Processor |

| TMS320C241PGS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Digital Signal Processor |

| TMS320C242 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DSP CONTROLLER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。