- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368671 > TMS320C242FNS 16-Bit Digital Signal Processor PDF資料下載

參數(shù)資料

| 型號(hào): | TMS320C242FNS |

| 元件分類: | 數(shù)字信號(hào)處理 |

| 英文描述: | 16-Bit Digital Signal Processor |

| 中文描述: | 16位數(shù)字信號(hào)處理器 |

| 文件頁數(shù): | 15/66頁 |

| 文件大小: | 803K |

| 代理商: | TMS320C242FNS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁

TMS320C242

DSP CONTROLLER

SPRS063B – DECEMBER 1997 – REVISED DECEMBER 1999

15

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251–1443

digital I/O control registers

Table 4 lists the registers available in the digital I/O module. As with other ’C242 peripherals, the registers are

memory-mapped to the data space.

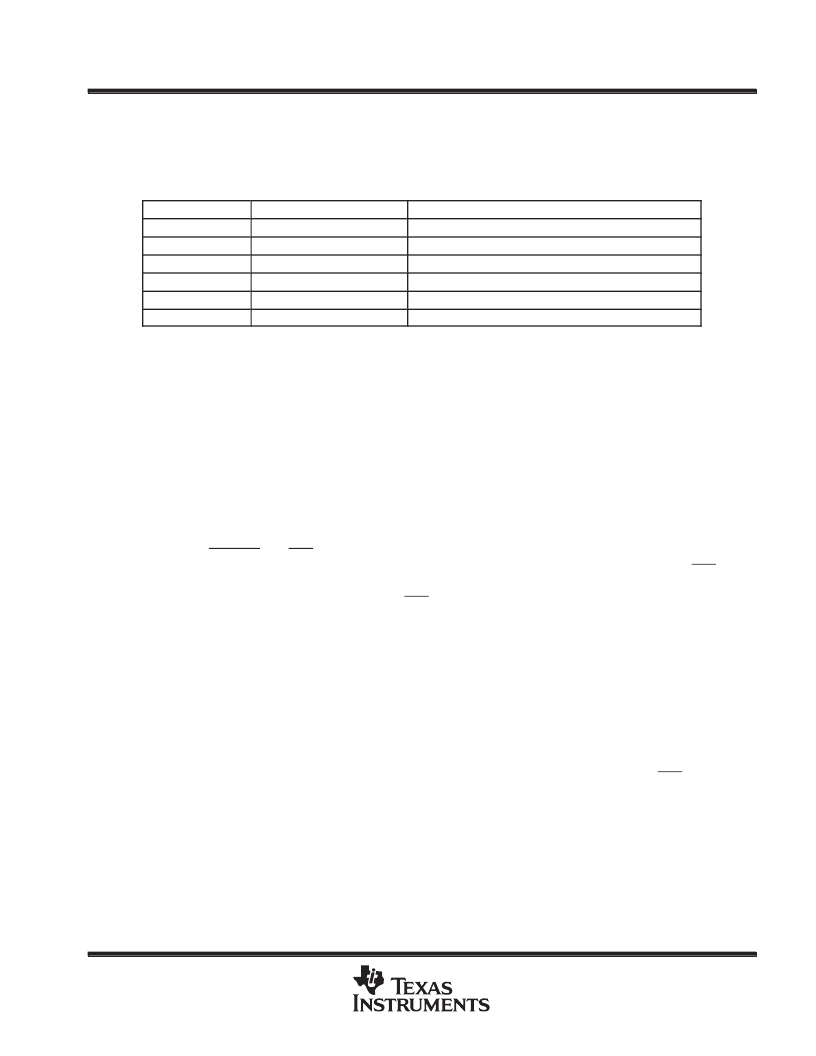

Table 4. Addresses of Digital I/O Control Registers

ADDRESS

REGISTER

NAME

7090h

OCRA

I/O mux control register A

7092h

OCRB

I/O mux control register B

7098h

PADATDIR

I/O port A data and direction register

709Ah

PBDATDIR

I/O port B data and direction register

709Ch

PCDATDIR

I/O port C data and direction register

709Eh

PDDATDIR

I/O port D data and direction register

device reset and interrupts

The TMS320x24x software-programmable interrupt structure supports flexible on-chip and external interrupt

configurations to meet real-time interrupt-driven application requirements. The ’C242 recognizes three types of

interrupt sources:

Reset

(hardware- or software-initiated) is unarbitrated by the CPU and takes immediate priority over any

other executing functions. All maskable interrupts are disabled until the reset service routine enables them.

The ’C242 device has two sources of reset: an external reset pin and a watchdog timer timeout (reset).

Hardware-generated interrupts

are requested by external pins or by on-chip peripherals. There are two

types:

–

External interruptsare generated by one of four external pins corresponding to the interrupts XINT1,

XINT2, PDPINT, and NMI. The first three can be masked both by dedicated enable bits and by the CPU’s

interrupt mask register (IMR), which can mask each maskable interrupt line at the DSP core. NMI, which

is not maskable, takes priority over peripheral interrupts and software-generated interrupts. It can be

locked out only by an already executing NMI or a reset.

–

Peripheral interrupts

are initiated internally by these on-chip peripheral modules: the event manager,

SCI, WD, and ADC. They can be masked both by enable bits for each event in each peripheral and by the

CPU’s IMR, which can mask each maskable interrupt line at the DSP core.

Software-generated interrupts

for the ’C242 include:

–

The INTR instruction.This instruction allows initialization of any ’C242 interrupt with software. Its

operand indicates the interrupt vector location to which the CPU branches. This instruction globally

disables maskable interrupts (sets the INTM bit to 1).

–

The NMI instruction.This instruction forces a branch to interrupt vector location 24h, the same location

used for the nonmaskable hardware interrupt NMI. NMI can be initiated by driving the NMI pin low or by

executing an NMI instruction. This instruction globally disables maskable interrupts.

–

The TRAP instruction.This instruction forces the CPU to branch to interrupt vector location 22h. The

TRAP instruction does notdisable maskable interrupts (INTM is not set to 1); therefore, when the CPU

branches to the interrupt service routine, that routine can be interrupted by the maskable hardware

interrupts.

–

An emulator trap. This interrupt can be generated with either an INTR instruction or a TRAP instruction.

A

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMS320C242PGA | 16-Bit Digital Signal Processor |

| TMS320C242PGS | 16-Bit Digital Signal Processor |

| TMS320C30GEL | 32-Bit Digital Signal Processor |

| SM320C25FJM | 16-Bit Digital Signal Processor |

| SM320C25GBM | 16-Bit Digital Signal Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMS320C242PG | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DSP CONTROLLER |

| TMS320C242PGA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Digital Signal Processor |

| TMS320C242PGS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Digital Signal Processor |

| TMS320C25 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:SECOND-GENERATION DIGITAL SIGNAL PROCESSORS |

| TMS320C25/-33/-50 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Digital Signal Processor |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。