- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382674 > TPS1100YPW (Texas Instruments, Inc.) SINGLE P-CHANNEL ENHANCEMENT-MODE MOSFETS PDF資料下載

參數(shù)資料

| 型號: | TPS1100YPW |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | SINGLE P-CHANNEL ENHANCEMENT-MODE MOSFETS |

| 中文描述: | 單P溝道增強(qiáng)型MOSFET |

| 文件頁數(shù): | 1/10頁 |

| 文件大?。?/td> | 155K |

| 代理商: | TPS1100YPW |

TPS1100, TPS1100Y

SINGLE P-CHANNEL ENHANCEMENT-MODE MOSFETS

SLVS078C – DECEMBER 1993 – REVISED AUGUST 1995

1

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

Low r

DS(on)

. . . 0.18

Typ at V

GS

= –10 V

3 V Compatible

Requires No External V

CC

TTL and CMOS Compatible Inputs

V

GS(th)

= –1.5 V Max

Available in Ultrathin TSSOP Package (PW)

ESD Protection Up to 2 kV Per

MIL-STD-883C, Method 3015

description

The

enhancement-mode MOSFET. The device has

been optimized for 3-V or 5-V power distribution

in battery-powered systems by means of Texas

Instruments LinBiCMOS

process. With a

maximum V

GS(th)

of –1.5 V and an I

DSS

of only

0.5

μ

A, the TPS1100 is the ideal high-side switch

for low-voltage, portable battery-management

systems where maximizing battery life is a primary

concern. The low r

DS(on)

and excellent ac

characteristics (rise time 10 ns typical) make the

TPS1100 the logical choice for low-voltage

switching applications such as power switches for

pulse-width-modulated (PWM) controllers or

motor/bridge drivers.

TPS1100

is

a

single

P-channel

The ultrathin thin shrink small-outline package or

TSSOP (PW) version with its smaller footprint and

reduction in height fits in places where other

P-channel MOSFETs cannot. The size advantage

is especially important where board real estate is

at a premium and height restrictions do not allow

for a small-outline integrated circuit (SOIC)

package.

AVAILABLE OPTIONS

PACKAGED DEVICES

SMALL OUTLINE

(D)

CHIP FORM

(Y)

TA

PLASTIC DIP

(P)

–40

°

C to 85

°

C

The D package is available taped and reeled. Add an R suffix to device type (e.g.,

TPS1100DR). The PW package is available only left-end taped and reeled

(indicated by the LE suffix on the device type; e.g., TPS1100PWLE). The chip form

is tested at 25

°

C.

TPS1100D

TPS1100PWLE

TPS1100Y

Caution. This device contains circuits to protect its inputs and outputs against damage due to high static voltages or electrostatic

fields. These circuits have been qualified to protect this device against electrostatic discharges (ESD) of up to 2 kV according to

MIL-STD-883C, Method 3015; however, it is advised that precautions be taken to avoid application of any voltage higher than

maximum-rated voltages to these high-impedance circuits.

LinBiCMOS is a trademark of Texas Instruments Incorporated.

Copyright

1995, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

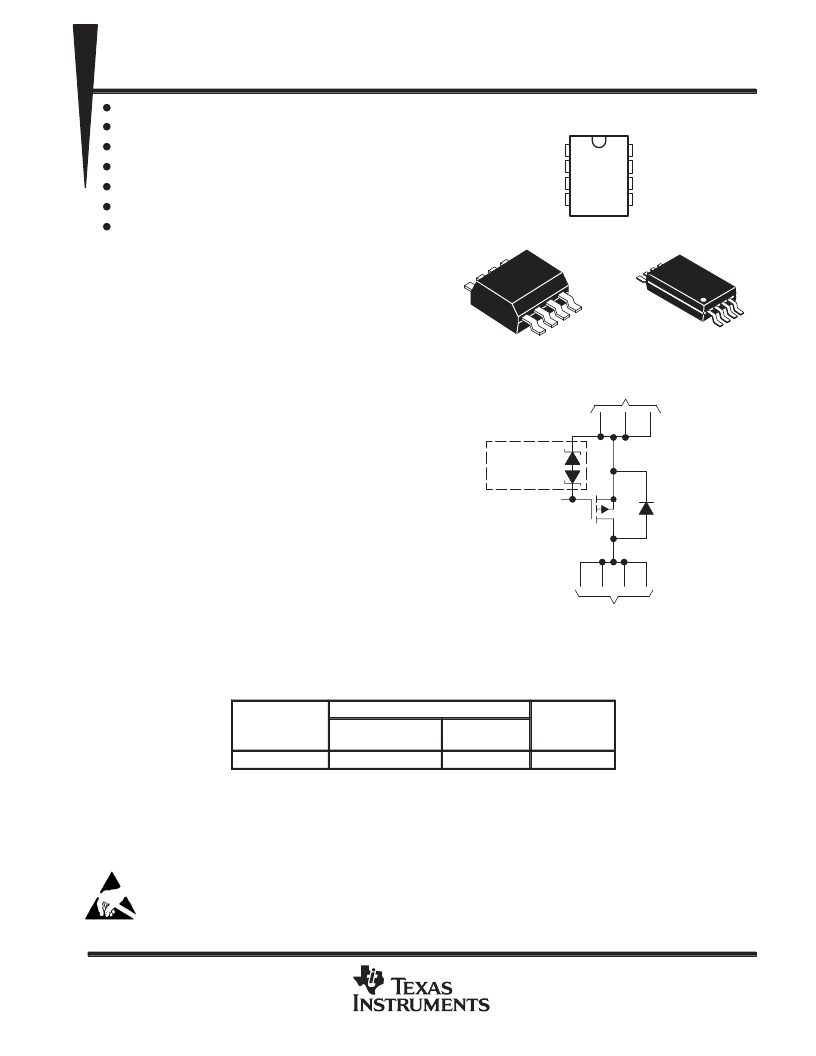

1

2

3

4

8

7

6

5

SOURCE

SOURCE

SOURCE

GATE

DRAIN

DRAIN

DRAIN

DRAIN

D OR PW PACKAGE

(TOP VIEW)

D PACKAGE

PW PACKAGE

SOURCE

DRAIN

GATE

ESD-

Protection

Circuitry

NOTE A: For all applications, all source pins should be connected

and all drain pins should be connected.

schematic

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TPS1100Y | CONNECTOR ACCESSORY |

| TPS1100YD | CONNECTOR ACCESSORY |

| TPS1101YPW | TELEPHONE CBL 8-CONDUCTOR1000 |

| TPS1101DW | CONNECTOR ACCESSORY |

| TPS1101PW | CONNECTOR ACCESSORY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TPS1101 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:SINGLE P-CHANNEL ENHANCEMENT-MODE MOSFETS |

| TPS1101_12 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:SINGLE P-CHANNEL ENHANCEMENT-MODE MOSFETS |

| TPS1101D | 功能描述:MOSFET Single P-Ch Enh-Mode MOSFET RoHS:否 制造商:STMicroelectronics 晶體管極性:N-Channel 汲極/源極擊穿電壓:650 V 閘/源擊穿電壓:25 V 漏極連續(xù)電流:130 A 電阻汲極/源極 RDS(導(dǎo)通):0.014 Ohms 配置:Single 最大工作溫度: 安裝風(fēng)格:Through Hole 封裝 / 箱體:Max247 封裝:Tube |

| TPS1101DG4 | 功能描述:MOSFET Single P-Ch Enh-Mode MOSFET RoHS:否 制造商:STMicroelectronics 晶體管極性:N-Channel 汲極/源極擊穿電壓:650 V 閘/源擊穿電壓:25 V 漏極連續(xù)電流:130 A 電阻汲極/源極 RDS(導(dǎo)通):0.014 Ohms 配置:Single 最大工作溫度: 安裝風(fēng)格:Through Hole 封裝 / 箱體:Max247 封裝:Tube |

| TPS1101DR | 功能描述:MOSFET Single P-Ch Enh-Mode MOSFET RoHS:否 制造商:STMicroelectronics 晶體管極性:N-Channel 汲極/源極擊穿電壓:650 V 閘/源擊穿電壓:25 V 漏極連續(xù)電流:130 A 電阻汲極/源極 RDS(導(dǎo)通):0.014 Ohms 配置:Single 最大工作溫度: 安裝風(fēng)格:Through Hole 封裝 / 箱體:Max247 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。