- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98279 > TPS2343DDPR (TEXAS INSTRUMENTS INC) 6-CHANNEL POWER SUPPLY SUPPORT CKT, PDSO80 PDF資料下載

參數(shù)資料

| 型號(hào): | TPS2343DDPR |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 電源管理 |

| 英文描述: | 6-CHANNEL POWER SUPPLY SUPPORT CKT, PDSO80 |

| 封裝: | GREEN, PLASTIC, HTSSOP-80 |

| 文件頁(yè)數(shù): | 3/42頁(yè) |

| 文件大小: | 942K |

| 代理商: | TPS2343DDPR |

第1頁(yè)第2頁(yè)當(dāng)前第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)

TPS2343

SLUS644B FEBRUARY 2005 MAY 2005

11

www.ti.com

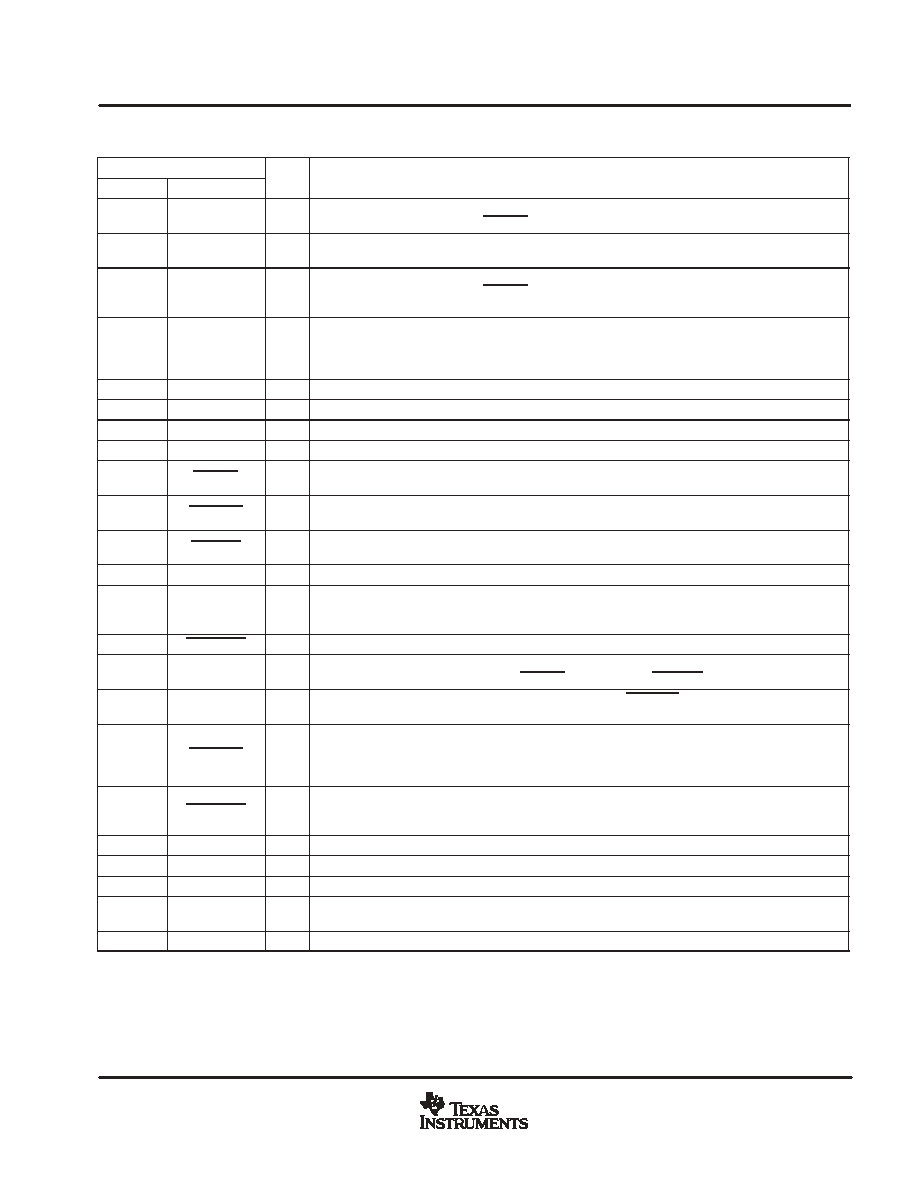

TERMINAL FUNCTIONS

TERMINAL

I/O

DESCRIPTION

NUMBER

NAME

I/O

DESCRIPTION

19

P12VOB

O

This output delivers 12-V power to slot B when enabled and is pulled to PWRGND by an internal

FET when PWRRNB is false or FAULTB is true.

20

M12VINB

I

Connect this power input to 12-V power to drive slot B. This input must be connected to M12VINA.

Connect a 0.1-

F capacitor from this pin to PWRGND.

21

M12VOB

O

This output delivers 12-V power to slot B when enabled and is pulled to PWRGND by an internal

FET when PWRRNB is false or FAULTB is true. Turn-on of 12-V power tracks turn-on of 12-V

power and is controlled by the capacitor on P12VGB.

22

MISET

I/O

This pin programs current limit for 12-V, 5-V, 3.3-V, and 12-V main supplies. MISET does not con-

trol 3.3VAUX or VIO current limit. The recommended resistor from MISET to ANAGND is 6.04 k

±1%. Increasing the value of this resistor raises the current-limit thresholds for the supplies listed

above proportionately. MISET resistor is 12 k

maximum.

23

ANAGND1

GND

Ground for low-level signals including the current sense circuits and the voltage reference.

24

PCIXCAP1B

O

This pin indicates bit 1 of the PCIXCAPB state.

25

DIGGND2

GND

This pin is the ground return for the digital circuits in the TPS2343.

26

PCIXCAP2B

O

This pin indicates bit 2 of the PCIXCAPB state.

27

FAULTB

O

This is an open-drain output that is low if there is a fault on the main power to slot B. This pin has

an internal 100-k

pull-up resistor to DIGVCC.

28

AUXFLTB

O

This open-drain output is low if there is a fault on VAUX power to slot B. This pin has an internal

100-k

pull-up resistor to DIGVCC and hysteresis.

29

OUTUVB

O

This open-drain output is low if slot B outputs are below normal operating range. This pin has an

internal 100-k

pull-up resistor to DIGVCC.

30

PCIXCAP3B

O

This pin indicates bit 3 of the PCIXCAPB state.

31

PCIXCAPB

I

This pin is the input to a 5-level A/D converter that determines the speed and mode of the inserted

B slot card based on the impedance from this pin to ANAGND. The operation of this pin meets the

specifications of the PCIX Local Bus Specification, revision 2.0.

32

PWROFFB

O

This output is low when all of the slot B power outputs are discharged.

33

PWRENB

I

This pin enables main power for slot B when high. This pin has an internal 100-k

pull-up resistor

to DIGVCC and hysteresis. When low, FAULTB is clearded and OUTUVB is asserted.

34

SWB

I

This input enables 3.3-V VAUX power to slot B. When low, AUXFLTB is cleared. This pin has an

internal 100-k

pull-up resistor to 3VAUXI and hysteresis.

35

ATTLEDB

O

This output is an open-drain power output that directly drives the slot B attention indicator LED. This

pin indicates the slot B LED attention indicator output signal from ALEDENB. This signal pulls low

with up to 24 mA of drive when asserted and is pulled high by an on-chip 100-k

resistor to V5IN

when deasserted.

36

PWRLEDB

O

This open-drain active-low power output directly drives the slot B power indicator LED. This pin

indicates the slot B power LED output from PLEDENB. This signal pulls low with up to 24 mA of

drive when asserted and is pulled high by an on-chip 100-k

resistor to V5IN when deasserted.

37

VIOSELB

I

This pin selects 3.3 V VIO for slot B when high, 1.5 V when low.

38

ALEDENB

I

This pin controls ATTLEDB. When this input is high, the LED is on (low).

39

PLEDENB

I

This pin controls PWRLEDB. When this input is high, the LED is on (low).

40

DIGVCC

I

This pin is the 3.3-V main power input to the TPS2343. Bypass this pin to DIGGND with a 0.1-

F

ceramic capacitor close to the TPS2343.

41

DIGGND1

GND

This pin is the ground return for the digital circuits in the TPS2343.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TPS2345PWNRND | 4-CHANNEL POWER SUPPLY SUPPORT CKT, PDSO24 |

| TPS2346PWG4 | 4-CHANNEL POWER SUPPLY SUPPORT CKT, PDSO24 |

| TPS2350DRG4 | 1-CHANNEL POWER SUPPLY SUPPORT CKT, PDSO14 |

| TPS2350PWG4 | 1-CHANNEL POWER SUPPLY SUPPORT CKT, PDSO14 |

| TPS2359RHHT | 2-CHANNEL POWER SUPPLY SUPPORT CKT, PQCC36 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TPS2343DDPRG3 | 功能描述:熱插拔功率分布 Dual Slot PCI-X 2.0 Hot-Plug Pwr Cntrlr RoHS:否 制造商:Texas Instruments 產(chǎn)品:Controllers & Switches 電流限制: 電源電壓-最大:7 V 電源電壓-最小:- 0.3 V 工作溫度范圍: 功率耗散: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MSOP-8 封裝:Tube |

| TPS2345PW | 功能描述:IC PWR MGR HOT SWAP 24-TSSOP RoHS:是 類別:集成電路 (IC) >> PMIC - 熱交換 系列:- 產(chǎn)品培訓(xùn)模塊:Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:100 系列:- 類型:熱插拔開(kāi)關(guān) 應(yīng)用:通用 內(nèi)部開(kāi)關(guān):是 電流限制:可調(diào) 電源電壓:9 V ~ 13.2 V 工作溫度:-40°C ~ 150°C 安裝類型:表面貼裝 封裝/外殼:10-WFDFN 裸露焊盤 供應(yīng)商設(shè)備封裝:10-TDFN-EP(3x3) 包裝:管件 |

| TPS2345PWR | 制造商:Rochester Electronics LLC 功能描述:COMPACTPCI HOT SWAP POWER MANAGER - Bulk |

| TPS2346PW | 功能描述:IC HOT SWAP POWER MGR 24-TSSOP RoHS:是 類別:集成電路 (IC) >> PMIC - 熱交換 系列:- 產(chǎn)品培訓(xùn)模塊:Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:100 系列:- 類型:熱插拔開(kāi)關(guān) 應(yīng)用:通用 內(nèi)部開(kāi)關(guān):是 電流限制:可調(diào) 電源電壓:9 V ~ 13.2 V 工作溫度:-40°C ~ 150°C 安裝類型:表面貼裝 封裝/外殼:10-WFDFN 裸露焊盤 供應(yīng)商設(shè)備封裝:10-TDFN-EP(3x3) 包裝:管件 |

| TPS2346PWR | 功能描述:熱插拔功率分布 Optical Network Hot Swap Controller RoHS:否 制造商:Texas Instruments 產(chǎn)品:Controllers & Switches 電流限制: 電源電壓-最大:7 V 電源電壓-最小:- 0.3 V 工作溫度范圍: 功率耗散: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MSOP-8 封裝:Tube |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。